סימולציית שרשרת אותות לאיסוף נתונים מפשטת את בחירת ובדיקת הרכיבים

באדיבות ‎DigiKey's North American Editors

2025-11-24

תכנון מערכת איסוף נתונים היה בעבר חיפוש אחר השילוב הנכון של רכיבים מתוך ערימת גיליונות נתונים ופתרון בעיות אבות-טיפוס שהורכבו יחד. כעת, המתכננים יכולים לחסוך זמן ותסכול בעזרת כלי תכנון דיגיטליים המאפשרים להם לבצע Drag-and-Drop של מודלים של רכיבים כמו חיישנים, בלוקי עיבוד אותות אנלוגיים, ממירי אנלוגי-לדיגיטלי (ADCs) ומסננים דיגיטליים לתוך שרשרת אותות וירטואלית. התוכנה מבצעת סימולציה של השרשרת הווירטואלית, ומאפשרת למתכנן לראות כיצד הרכיבים שנבחרו משפיעים על תוצאות כגון יחס אות-לרעש (SNR), שגיאת הגבר וממתח, והספקת-כוח.

חבילת התכנון הדיגיטלי Precision Studio של (Analog Devices, Inc. (ADI כוללת את Signal Chain Designer, מודול המסייע למתכננים לבצע סימולציה של מערכות איסוף הנתונים שלהם לפני בנייתן. ב-Signal Chain Designer, המשתמש בוחר חיישן, מגדיר פרמטרים עבור המודל, ולאחר מכן מכניס בלוקים של מעגלים המייצגים את הרכיבים בשרשרת האותות (איור 1).

איור 1: Signal Chain Designer בתוך Precision Studio של ADI מאפשר למתכננים לבחור חיישן, ולאחר מכן לבצע Drag-and-Drop של בלוקי מעגלים לתוך השרשרת כדי לבצע סימולציה של רכיבי איסוף הנתונים. (מקור התמונה: .Analog Devices, Inc)

איור 1: Signal Chain Designer בתוך Precision Studio של ADI מאפשר למתכננים לבחור חיישן, ולאחר מכן לבצע Drag-and-Drop של בלוקי מעגלים לתוך השרשרת כדי לבצע סימולציה של רכיבי איסוף הנתונים. (מקור התמונה: .Analog Devices, Inc)

אות החיישן חייב לעבור מספר שלבים במסעו להפוך לנתונים אמינים, וכל שלב מורכב מרכיב אחד או יותר של מעגל אלקטרוני או מעגל משולב (IC) המכין את האות לשלב הבא. הדרגות הנפוצות ביותר מגבירות את האות האנלוגי, מסננות את האות האנלוגי, ממירות את האות האנלוגי לדיגיטלי ומסננות את האות הדיגיטלי.

דרגת הגברת האות האנלוגי

אותות אנלוגיים הנוצרים על ידי חיישנים אינם תואמים לעיתים קרובות לכניסות האופטימליות של מערכת איסוף הנתונים. דרגת הגברת האות האנלוגי משתמשת במגברי שרת (op amps), מגברים דיפרנציאליים במלואם וייחוסי מתח, כמו גם רכיבים פסיביים כמו נגדים, קבלים ומשרנים, כדי להמיר את אות החיישן לצורה יעילה עבור מערכת איסוף הנתונים.

ב-Signal Chain Designer, המשתמש מציין את סוגי הכניסה והיציאה של דרגת ההגברה האנלוגית, את ההגבר הנדרש ואת הסטת הרמה הנדרשת כדי להשיג את מתח הכניסה הנכון. לאחר מכן התוכנה יוצרת מעגל העומד בפרמטרים שצוינו באמצעות מוצרי ADI ומפיקה סכמה.

לדוגמה, עבור החיישן המשמש באיור 1 עם אימפדנס של kΩ 1 ב-kHz 1 וקיבוליות של pF 100, המשתמש יכול להגדיר הגבר של V/V 2 והסטת רמה של V 2.5 (איור 2).

איור 2: משתמשי Signal Chain Designer מגדירים את התצורה, ההגבר, הסטת הרמה ופרמטרים אחרים של דרגת הגברת האות האנלוגי. (מקור התמונה: .Analog Devices, Inc)

איור 2: משתמשי Signal Chain Designer מגדירים את התצורה, ההגבר, הסטת הרמה ופרמטרים אחרים של דרגת הגברת האות האנלוגי. (מקור התמונה: .Analog Devices, Inc)

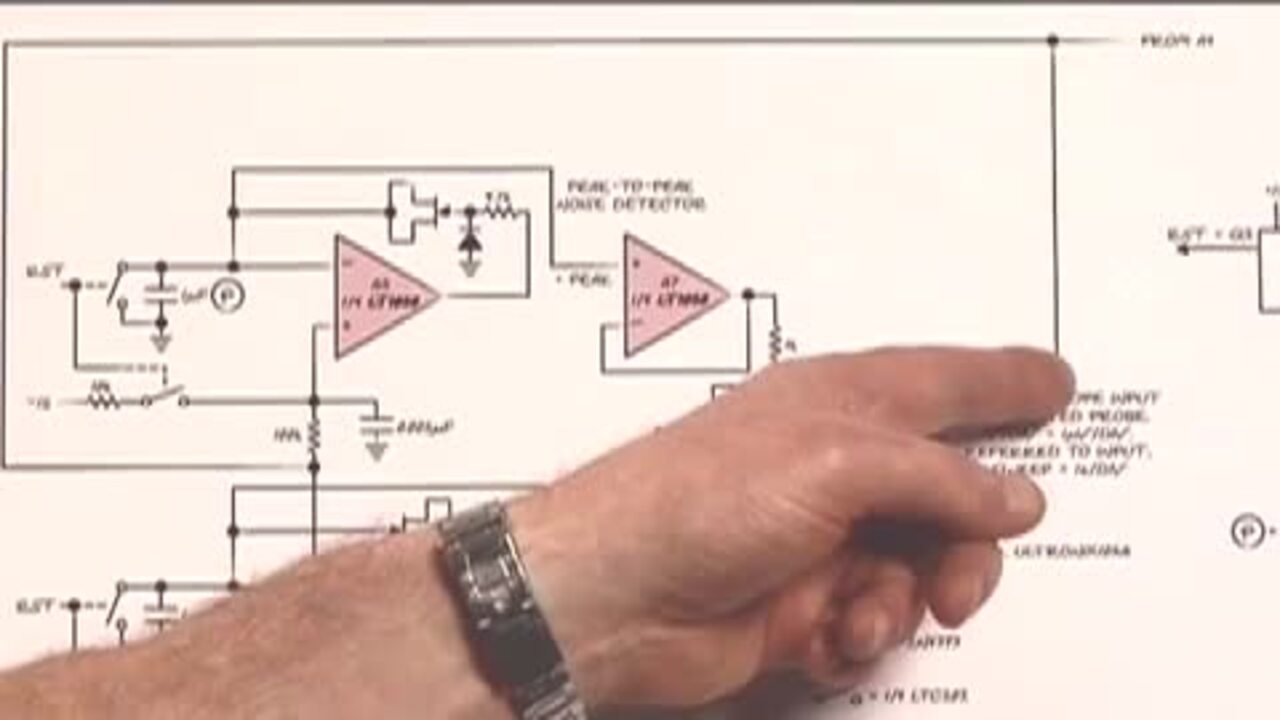

על בסיס פרמטרים אלה, התוכנה בונה סכמת מעגל עבור דרגת הגברת האות האנלוגי (איור 3, למעלה) המכיל את מגבר שרת ADA4097-2. מגברי שרת במשפחת ADA4097-2 דורשים רק µA 32.5 לכל ערוץ כדי להשיג מכפלת הגבר-רוחב-פס (GBP) של kHz 130 עבור הגבר מתח אות גדול, עם רעש שיא-לשיא (P-P) של nV 1,000 בין Hz 0.1 ו-Hz 10 ופינת רעש f/1 טיפוסית ב-Hz 6

התוכנה מפתחת גם מעגל ייחוס עבור דרגת המגבר עם ייחוס מתח Bandgap מדויק LTC6655B-2.5 ומגבר שרת AD8510 (איור 3, למטה), שניהם של ADI.

איור 3: סכמות מעגל של דרגת הגברת אותות אנלוגיים של ה-Signal Chain Designer המבוססות על מפרטי המשתמש וכוללות רכיבים אלקטרוניים מתאימים של ADI. (מקור התמונה: .Analog Devices, Inc)

איור 3: סכמות מעגל של דרגת הגברת אותות אנלוגיים של ה-Signal Chain Designer המבוססות על מפרטי המשתמש וכוללות רכיבים אלקטרוניים מתאימים של ADI. (מקור התמונה: .Analog Devices, Inc)

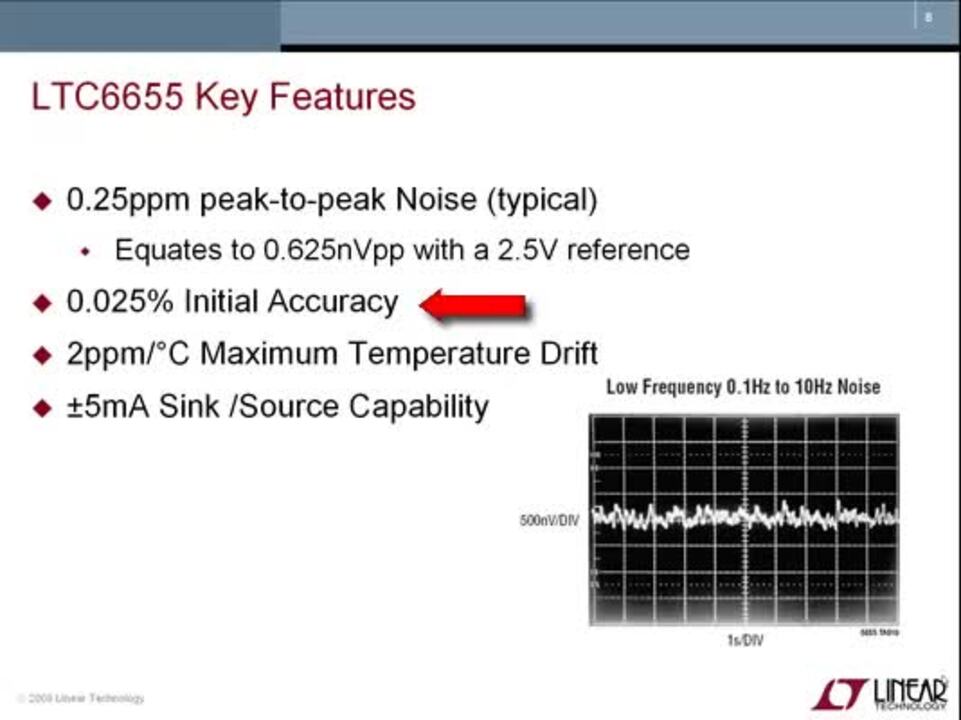

ל-LTC6655B-2.5 יש רעש P-P של nV 625 עבור P-P של ppm 0.25 בין Hz 0.1 ו-Hz 10, דיוק מקסימלי של ±0.025% וסחיפת מתח נמוכה של ppm/°C 2 לכל היותר, מה שמבטיח שהוא מפיק מתח אות יציב ללא תלות בשינויי מתח הכניסה והעומס. למגבר השרת JFET (טרנזיסטור אפקט שדה צומת) AD8510 יש בדרך כלל רעש ספקטרלי של nV 8 בתדר של kHz 1, הוא דורש רק pA 25 של זרם ממתח כניסה, והוא מתייצב ברצועת שגיאה של %0.1 בתוך ns 500.

ה-Signal Chain Designer מאפשר למשתמש גם לציין כיצד לאכשר אותות בדרגה זו. המשתמשים יכולים להגדיר במלואם מגברים דיפרנציאליים, מגברי מכשור או מגברי חישת זרם.

דרגת סינון אותות אנלוגיים

לאחר מכן יש לסנן את האות האנלוגי המוגבר כדי להסיר רעשים ועיוותים הנוצרים על ידי ההגברה. מסננים יכולים להשתמש ברכיבים פסיביים כמו נגדים וקבלים כדי ליצור מסננים מסדר-ראשון בעלי ירידות מתונות של dB/decade 20- לאחר תדר הקיטעון. מסננים מסדר-שני ומעלה הם בדרך כלל מסננים אקטיביים המשתמשים במגבר שרת אחד או יותר כדי להשיג ירידות חדות יותר.

תצורת המסנן תקבע אם הוא מנחית תדרים מעל לתדר המרכזי, 0f (מעביר נמוכים), מתחת ל-0f (מעביר גבוהים), מחוץ לשני תדרי הקיטעון (מעביר פס), או מחוץ לפס תדרים ספציפי (חוסם-פס או Notch). פרמטרים אחרים של המסנן, כמו גורם Q, משפרים עוד יותר את תגובת המסנן, מגדירים את חדות הירידות, התנהגות טרנזיינט וצורת הפס המעביר.

ב-Signal Chain Designer המשתמשים יכולים להגדיר את הפרמטרים עבור מסננים פשוטים על ידי בחירת סוג המסנן והגדרת הפרמטרים העיקריים. ה-Filter Wizard של ה-Signal Chain Designer יכול גם לתכנן מסננים פשוטים באמצעות מסננים מסדר-שלישי ומעלה ולייבא את המסנן בחזרה לתכן שרשרת האותות הדיגיטלית. בדוגמה (איור 4), המשתמש בוחר במסנן מעביר נמוכים עם 0f של kHz 10 וגורם Q של 0.707. המסנן מסוג Sallen-Key שנבחר משתמש במגבר שרת יחיד כדי לקבל אימפדנס כניסה גבוה ולהפיק אות בעל אימפדנס נמוך עם יציבות טובה.

איור 4: המשתמשים מגדירים את הפרמטרים של דרגת סינון אנלוגי ב-Signal Chain Designer, כולל סוג המסנן, 0f, גורם Q וההגבר. (מקור התמונה: .Analog Devices, Inc)

איור 4: המשתמשים מגדירים את הפרמטרים של דרגת סינון אנלוגי ב-Signal Chain Designer, כולל סוג המסנן, 0f, גורם Q וההגבר. (מקור התמונה: .Analog Devices, Inc)

בעזרת פרמטרים אלה, ה-Signal Chain Designer מפיק מעגל הכולל את מגבר השרת פס-לפס LT6020 של ADI (איור 5). ה-LT6020 צורך פחות מ-µA 100 אך עדיין יכול להגיב במהירות לשינויים באות הכניסה עם קצב שינוי (Slew Rate) של µs/V 5. יש לו GBP של kHz 400 בתחום הטמפרטורות שלו של C°40- עד Cִ°125+.

איור 5: תרשים המעגל של דרגת מסנן אות אנלוגי שהופק על ידי ה-Signal Chain Designer, עם מגבר שרת LT6020 עם קצב שינוי מהירות גבוה וצריכת הספק נמוכה כמסנן מעביר נמוכים מסדר-שני Sallen-Key. (מקור התמונה: .Analog Devices, Inc)

איור 5: תרשים המעגל של דרגת מסנן אות אנלוגי שהופק על ידי ה-Signal Chain Designer, עם מגבר שרת LT6020 עם קצב שינוי מהירות גבוה וצריכת הספק נמוכה כמסנן מעביר נמוכים מסדר-שני Sallen-Key. (מקור התמונה: .Analog Devices, Inc)

דרגת המרה אנלוגי-לדיגיטלי

השלב האחרון במסעו של האות מתגובת החיישן ועד לנתונים הוא המרת האות האנלוגי לצורה דיגיטלית. ארכיטקטורות ADC נפוצות כוללות רגיסטר קירוב עוקב (SAR) עבור רזולוציה טובה בקצב דגימה בינוני, ו-(Delta-Sigma (ΔΣ עבור רזולוציה גבוהה במהירויות דגימה נמוכות יותר. כדי להשיג את היציאה הדיגיטלית הרצויה, על המתכננים לדעת את סוג הכניסה, רזולוציית המערכת וקצב נתוני היציאה.

המשתמשים מגדירים פרמטרים אלה ב-Signal Chain Designer, והתוכנה מפיקה מעגל ADC הכולל ייחוס מתח ומסנן התנגדותי/קיבולי פסיבי (RC) בכניסה. חלק מממירי ה-ADC מאפשרים גם למשתמשים לשלב סינון דיגיטלי או להגדיר את ממירי ה-ADC לאופן אימפדנס גבוה (Hi-Z) עבור תכנים פשוטים יותר בהספק נמוך יותר.

בדוגמה (איור 6), היציאה של ה-Signal Chain Designe הגדירה את ייחוס המתח ADR4525 ואת ה-ΔΣ ADC AD7175-2 של ADI. ל-ADR4525 יש יציבות טמפרטורה טובה עם מקדמי טמפרטורה בין ppm/°C 0.8 ו-ppm/°C 4.0, ורעש יציאה P-P של µV 1 ב-OUTV 2.048 ו-Hz 0.1 עד Hz 10. ה-AD7175-2 הוא ADC bit-24 עם תפוקה של 250,000 דגימות בשנייה (kSPS 250) וזמן התייצבות של µs 20.

איור 6: בדרגת ההמרה אנלוגי-לדיגיטלי, תרשים המעגל של ה-Signal Chain Designer כולל מסנן כניסה RC פסיבי, ייחוס מתח ומודול ADC. (מקור התמונה: .Analog Devices, Inc)

איור 6: בדרגת ההמרה אנלוגי-לדיגיטלי, תרשים המעגל של ה-Signal Chain Designer כולל מסנן כניסה RC פסיבי, ייחוס מתח ומודול ADC. (מקור התמונה: .Analog Devices, Inc)

בכל דרגה בשרשרת האותות, המשתמש יכול לצפות בטבלת מוצרים המציגה רכיבים חלופיים מתאימים. לדוגמה, מתכנן עשוי לבחור להחליף SAR ADC כגון AD4008 ב-ΔΣ ADC המוצג בדוגמה. ה-AD4008 צורך בין µW 70 ב-kSPS 10 ו-mW 14 ב-MSPS 2, ההספק המקסימלי שלו. פעולה פסאודו-דיפרנציאלית מאפשרת דיוק של bit-16 עם תכן פשוט באופן Hi-Z.

לאחר המרה אנלוגית-לדיגיטלית, המתכננים יכולים למטב את היציאה על ידי הוספת בלוקי מסנן דיגיטליים לתוך התכן במורד הזרם של ה-ADC ב-Signal Chain Designer. האפשרויות בבלוקים של סינון דיגיטלי אלה כוללות ממוצעים, מסננים מסדר-ראשון ו-שני, ומסנני CIC פשוטים של ממוצע-נע.

לאחר בניית מערכת איסוף נתונים וירטואלית באמצעות ה-Signal Chain Designer, המשתמשים יכולים לבצע סימולציה של תגובת התדר, רעש, תקציב שגיאות DC, הספק ותחומי כניסה מתוך התוכנה. עבור סימולציות יותר מותאמות-במיוחד, ה-Signal Chain Designer יכול ליצור מערכי בדיקה וירטואליים שניתן לערוך ולהפעיל ב-LTspice.

סיכום

כלים דיגיטליים כמו Signal Chain Designer של ADI יכולים למזער את הניחושים והתסכול הכרוכים בבניית מערכת איסוף נתונים מדויקת. עם דגמים של מגוון רחב של מגברי שרת, ייחוסי מתח, ממירי ADC ורכיבים אחרים הזמינים בתוך התוכנה, Signal Chain Designer מאפשר למשתמשים לכוונן את מערכות איסוף הנתונים שלהם באופן וירטואלי, ומבטיח מעבר חלק לרכישה ופריסת החומרה.

מיאון אחריות: דעות, אמונות ונקודות מבט המובעות על ידי מחברים שונים ו/או משתתפי פורום באתר אינטרנט זה לא בהכרח משקפות את הדעות, האמונות ונקודות המבט של חברת DigiKey או את המדיניות הרשמית של חברת DigiKey.