כיצד לפרוס בינה מלאכותית בקצה על גבי מערכי FPGA בעזרת כלים מוכרים

באדיבות ‎DigiKey's North American Editors

2026-02-17

בינה מלאכותית (AI) בקצה הרשת (EDGE AI) לעיתים רחוקות פירושה רק הסקת מסקנות. פריסות בעולם האמיתי כוללות בדרך כלל כניסה/יציאה (I/O) מהירות-גבוהה, התאמת אותות וחוגי בקרה זמן-אמת, שכולן פועלות בו זמנית. עומסי עבודה רב-תפקודיים אלה דורשים תיאום הדוק ורמות דטרמיניזם שמתכננים מתקשים לעמוד בהם באמצעות חומרת בינה מלאכותית מהזרם המרכזי.

שני גורמים מחמירים את הבעיה. ראשית, מודלים של בינה מלאכותית מתפתחים בקצב מסחרר, מה שדוחף מעצבים לאמץ פלטפורמות התומכות בעדכוני אלגוריתמים מהירים. במקביל, מערכות קצה רבות נשארות בשטח במשך עשור או יותר, מה שמקשה על הבטחת יכולת הסתגלות לטווח ארוך. שנית, המסלול ממודל מאומן למערכת פרוסה נותר מקוטע. מדעני נתונים עובדים ב-PyTorch וב-TensorFlow, בעוד שצוותים משובצים משתמשים בשרשראות כלים שונות לחלוטין, מה שיוצר חיכוך במהלך מסירות המאט את זמן ההגעה לייצור.

עמידה באתגרים אלה דורשת פלטפורמות המשלבות עיבוד בינה מלאכותית בעל תפוקה גבוהה עם התנהגות דטרמיניסטית, כניסה/יציאה גמישה ויכולת הסתגלות ארוכת טווח, והכל במסגרת מעטפת הספק מוגבלת האופיינית לפריסות קצה.

מאמר זה מדגיש את היישומים ואת הדרישות הנלוות המאתגרים מתכננים לחקור ארכיטקטורות חדשות של בינה מלאכותית בקצה. לאחר מכן, הוא מציג התקני FPGA (מערך שערים ניתנים לתכנות בשטח) מבוססי AI בקצה וכלי תוכנה של Altera, ומראה כיצד ניתן להשתמש בהם כדי לענות על הצרכים של יישומים אלה במגוון רחב של ביצועים ונקודות הספק.

התפתחות בינה מלאכותית בקצה דורשת חדשנות אדריכלית

מערכות קצה משתמשות יותר ויותר בטכניקות מגוונות של בינה מלאכותית, למידת מכונה (ML) קלאסית לגילוי אנומליות, רשתות עצביות קונבולוציוניות (CNNs) לתפיסה, ושנאים עבור מודלי שפה גדולים (LLMs). אלגוריתמים עתירי מחשוב אלה מתקיימים לעתים קרובות במקביל לפונקציות תובעניות שאינן קשורות לבינה מלאכותית, כגון עיבוד אותות, רשתות ובקרה בזמן אמת.

מערכות אוטונומיות הן דוגמה מצוינת. לעתים קרובות הם צריכים לקלוט נתונים ממספר מודלים של חיישנים (למשל, וידאו, אודיו, מכ"ם, LiDAR ומשוב תנועה/מיקום), לעבד מראש זרמים אלה בתפוקה גבוהה, לנתח את התוצאות באמצעות בינה מלאכותית מתוחכמת, ולאחר מכן לנהל חוגי בקרה מדויקים, והכל עם דטרמיניזם אמין.

דוגמאות דומות רבות ניתן למצוא ביישומי אוטומציה תעשייתית, הדמיה רפואית, הגנה ותקשורת. מוטיב חוזר הוא שעומסי העבודה המתכנסים הם מאתגרים להכלה באמצעות ארכיטקטורות מסורתיות.

כיצד רכיבי FPGA מתאימים באופן ייחודי לבינה מלאכותית בקצה

לעומת זאת, דרישות אלו תואמות היטב ליכולותיהם של רכיבי FPGA. במקורם, רכיבי FPGA מספקים לוגיקה ניתנת להגדרה המבצעת פעולות במקביל באמת, עם התנהגות תזמון אפויה בזמן התכנון במקום להשתנות במהלך זמן הריצה. ארכיטקטורה זו מאפשרת דטרמיניזם בעל השהייה נמוכה, החיוני לבינה מלאכותית בקצה. הלוגיקה הגמישה ממנפת גם I/O עוצמתי: רכיבי FPGA מציעים בדרך כלל שפע של I/O מהירות-גבוהה שיכולות להתממשק עם מגוון רחב של חיישנים ומפעילים, ומספקות צימוד הדוק עם עיבוד בינה מלאכותית.

רכיבי FPGA מכילים גם זיכרון פנימי מבוזר, ששומר על נתונים קרוב ללוגיקה הפועלת עליהם. זה מפחית את צווארי הבקבוק הנוצרים כששלבי עיבוד מרובים חייבים להתחרות על גישה לאפיק זיכרון משותף, אילוץ נפוץ בארכיטקטורות מבוססות מעבד.

רכיבי FPGA רבים משלבים גם חומרה מיוחדת לעיבוד אותות דיגיטליים (DSP). מעגלים מוקשים אלה מספקים ביצועים גבוהים יותר ויעילות אנרגיה טובה יותר עבור עומסי עבודה של עיבוד אותות בהשוואה למארג לשימוש כללי. חלק מרכיבי ה-FPGA משלבים גם מערכות מעבדים קשיחות היכולות להריץ מחסניות תוכנה סטנדרטיות, כולל Linux, מה שמאפשר פיתוח תוכנה קונבנציונלית עבור משימות כמו רשתות, ניהול התקנים וממשקי משתמש.

בקיצור, רכיב FPGA יחיד יכול לאחד פונקציות שאחרת היו דורשות שבבי I/O נפרדים, מאיצי בינה מלאכותית, מעבדי DSP ומעבדי Control-Plane. התוצאה יכולה להיות רשימת חומרים (BOM) מופחתת, חתימת שטח לוח קטנה יותר וצריכת הספק נמוכה יותר, תוך שמירה על השהייה נמוכה ודטרמיניזם שנדרשים על ידי יישומי בינה מלאכותית בקצה.

כיצד הוספת בלוקי טנזור של בינה מלאכותית פותחת אפשרויות חדשות

חומרת FPGA DSP מסורתית כבר מתאימה היטב לעומסי עבודה רבים בקצה, אך הסקת מסקנות של בינה מלאכותית נוטה להתאפיין בביצוע פעולות כפל-צבירה דחוסות אך בדיוק נמוך. כדי לטפל בכך, התקני Agilex 3 ו-Agilex 5 של Altera כוללים DSP משופר עם בלוקי טנזור של בינה מלאכותית. זוהי חומרה ייעודית להכפלות מטריצה-מטריצה ווקטור-מטריצה, שמופיעות שוב ושוב בגרפי חישוב של בינה מלאכותית.

בלב גישה זו נמצאים מכפלה סקלרית ומנוע מחבר/צובר (איור 1). במצב טנזור, מנוע המכפלה הסקלרית (dot engine) המובנה מבצע מכפלה של 10 אלמנטים באמצעות קלט של 8 סיביות ומשקלים של 8 סיביות טעונים מראש. כדי להרחיב את הטווח הדינמי, נתיב הנתונים יכול גם להשתמש ב"מעריך משותף" משותף עבור קנה מידה בסגנון נקודה צפה של בלוקים, ובכך לטפל בתרחיש הטיפוסי שבו הסקה של בינה מלאכותית דורשת טווח דינמי גבוה אך דיוק נמוך.

איור 1: בלוק הטנזור של בינה מלאכותית יכול לבצע מכפלות סקלריות של 10 אלמנטים. (מקור תמונה: Altera)

איור 1: בלוק הטנזור של בינה מלאכותית יכול לבצע מכפלות סקלריות של 10 אלמנטים. (מקור תמונה: Altera)

תוצאת המכפלה הסקלרית היא ברוחב 32 סיביות (נקודה קבועה או נקודה צפה בדיוק יחיד), וניתן לשרשר אותה לשלב חיבור/צבירה נוסף כדי לחשב מכפלות סקלריות גדולות יותר על פני בלוקים סמוכים. כל בלוק טנזור של בינה מלאכותית כולל שתי עמודות של מכפלה סקלרית, המאפשרות מגוון מצבי פעולה.

במקרה שימוש טיפוסי, חלק מחומרת המתמטיקה המשופרת משמש בתפקיד ה-DSP המסורתי שלה, כגון ביצוע טרנספורמציות פורייה מהירות (FFTs) על נתוני מכ"ם. חלקים אחרים משמשים כבלוקי טנזור של בינה מלאכותית, כגון CNN לביצוע זיהוי אובייקטים. גמישות זו היא קריטית עבור מערכות קצה שחייבות להתמודד עם בינה מלאכותית לצד פונקציות אחרות עתירות מחשוב.

מגוון אפשרויות FPGA עבור עומסי עבודה שונים של בינה מלאכותית

משפחות ה-Agilex מספקות גם גמישות ניכרת במדרג ביצועים. החלקים נעים מהתקנים ממוקדי יעילות במידות של 12 מ"מ × 12 מ"מ בלבד ועד גרסאות בעלות ביצועים גבוהים המספקות עד 152.6 טרה-פעולות שיא לשנייה (TOPS), עם מדרוג דומה ביכולות I/O וממשק זיכרון.

דוגמה לחלק בעל ביצועים גבוהים היא ה-Agilex 5 A5ED065BB32AE4SR0, שמספק 22.17 TOPS במארז של 32 × 32 מ"מ. דוגמה לחלק מכוון יעילות היא ה-Agilex 3 A3CW135BM16AE6S, שמספק 2.8 TOPS במארז של 16 × 16 מ"מ. המפרטים העיקריים עבור כל אחת מהן מוצגים בטבלה 1.

|

טבלה 1: מוצגים כמה מפרטים עיקריים עבור רכיבי FPGA דוגמה Agilex 5 ו-Agilex 3. (מקור טבלה: Altera (מותאמת על ידי המחבר))

שתי המשפחות זמינות כרכיבי FPGA מסורתיים או כמערכות על שבב (SoCs) עם מעבדי Arm משולבים. מערכות על שבב Agilex 3 משלבות מעבד Arm Cortex-A55 בעל שתי ליבות, 800 מגה-הרץ (MHz). מערכות על שבב Agilex 5 כוללות אשכול אסימטרי עם שתי ליבות Cortex-A76 של 1.8 ג'יגה-הרץ (GHz) לצד שתי ליבות 1.5 GHz Cortex-A55. שתי התצורות תומכות ב-Linux, מה שמאפשר פיתוח תוכנה קונבנציונלית עבור רשתות, ניהול התקן וממשקי משתמש.

פישוט פריסת בינה מלאכותית בקצה תוך שימוש ברכיבי FPGA

מודלים של בינה מלאכותית מפותחים בדרך כלל בסביבות עבודה ממוקדות תוכנה עם מחזורי פיתוח מהירים, בעוד שמימושים ב-FPGA דרשו היסטורית מיומנויות פיתוח חומרה ומחזורי אינטגרציה ארוכים יותר. FPGA AI Suite של Altera (איור 2) מספקת נתיב ישיר יותר ממודל מאומן לקניין רוחני (IP) ניתן לפריסה של הסקה ב-FPGA, באמצעות תהליך עבודה התואם לכלי הבינה המלאכותית הסטנדרטיים בתעשייה.

איור 2: תהליך העבודה של FPGA AI Suite מגשר בין סביבות עבודה סטנדרטיות של בינה מלאכותית לפריסת FPGA. (מקור תמונה: Altera)

איור 2: תהליך העבודה של FPGA AI Suite מגשר בין סביבות עבודה סטנדרטיות של בינה מלאכותית לפריסת FPGA. (מקור תמונה: Altera)

ניתן לסכם את תהליך העבודה כדלקמן:

- פיתוח מודל ההסקה בסביבת עבודה סטנדרטית כגון PyTorch, TensorFlow או ONNX.

- השתמש בערכת הכלים OpenVINO כדי להמיר את המודל לייצוג ביניים (IR) הכולל קובץ גרף (.xml) ומשקולות (.bin).

- העבר את תוצרי ה-IR אל ה-FPGA AI Graph Compiler, שממפה את המודל על גבי משאבי ה-FPGA הזמינים. משאבים כאלה יכולים לכלול מעבד מארח חיצוני, מעבד פנימי או תצורת Headless.

- הדר ופרוס את השכבות המתקבלות באמצעות Quartus Prime Pro Edition, כאשר הריצה מנוהלת דרך מחסנית התוכנה של מנוע ההסקה וממשקי תכנות יישומים (APIs) של ה-FPGA AI עבור תנועת זיכרון ותזמון חומרה.

- כחלק מתהליך ההידור (compilation), השתמש ב-Architecture Optimizer כדי לאזן בין ביצועים לבין ניצול משאבים. לדוגמה, השתמש בו כדי להבטיח שהמימוש עומד ביעדי תפוקת ההסקה (inference throughput) תוך השארת מקום ללוגיקת FPGA אחרת.

במונחים מעשיים, ערכה של גישה זו טמון בכך שהיא הופכת את ה"פריסה ב-FPGA" לתהליך של אינטגרציה, במקום למאמץ של תכנון מאיץ. מדעני נתונים יכולים להישאר בתוך תהליכי העבודה המוכרים לפיתוח מודלים, בעוד שצוותי ה-FPGA והמערכות המשובצות מקבלים תוצרים המשתלבים באופן טבעי במחזור הבנייה והפריסה, מה שמאפשר סבבי פיתוח מהירים יותר ככל שהמודלים והדרישות משתנים. מודלים שאומנו מראש, הזמינים דרך ה-Open Model Zoo עבור ערכת הכלים OpenVINO יכולים להאיץ עוד יותר את הפיתוח.

התחלה מהירה עם ערכות פיתוח קלות לשימוש

כדי להתחיל לחקור בינה מלאכותית בקצה (edge AI) על רכיבי FPGA, למתכננים יש מספר אפשרויות לערכות פיתוח. עבור יישומים בעלי ביצועים גבוהים יותר, ערכת הפיתוח Terasic P0775 Atum A5 (איור 3) היא בחירה טובה. בנויה סביב ה-Agilex 5 A5ED065BB32AE4SR0, הערכה מספקת מגוון רחב של ממשקים המתאימים למערכות בקצה הרשת. התכונות העיקריות כוללות 8 ג'יגה-בייט (Gbytes) של DDR4, יציאות +QSFP ו-2.5 ג'יגה-ביט (Gbit) Ethernet (GbE), ממשק PCIe Gen 3 x4, מחברי מצלמה MIPI כפולים ויציאת HDMI. הערכה כוללת רישיון חינמי עבור Quartus Prime Pro Edition.

איור 3: ערכת הפיתוח P0775 Atum A5 מספקת גישה לפיתוח בינה מלאכותית וראייה ממוחשבת ביצועים-גבוהים. (מקור תמונה: Terasic)

איור 3: ערכת הפיתוח P0775 Atum A5 מספקת גישה לפיתוח בינה מלאכותית וראייה ממוחשבת ביצועים-גבוהים. (מקור תמונה: Terasic)

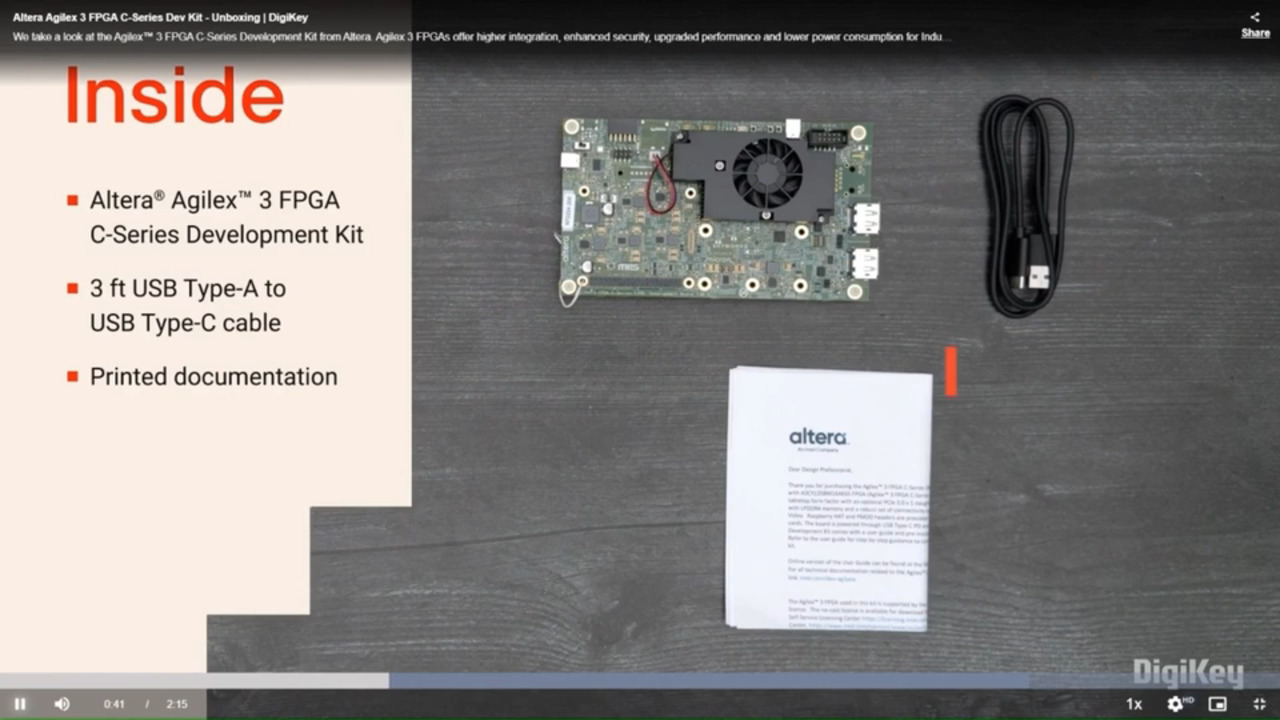

עבור יישומים ממוקדים ביעילות, מתכננים יכולים לפנות לערכת הפיתוח DK-A3W135BM16AEA Agilex 3 FPGA ו-SoC C-Series (איור 4). בנויה סביב ה-Agilex 3 A3CW135BM16AE6S, ערכה זו מדגישה אב טיפוס קומפקטי עם אפשרות הרחבה ידידותית למערכת אקולוגית. הלוח כולל 4 גיגה-בייט של LPDDR4, ממשקי GbE, יציאות DisplayPort ו-USB 2.0, יחד עם מחבר Raspberry Pi HAT וממשק Digilent Pmod להרחבה פשוטה ומהירה.

איור 4: ערכת הפיתוח Altera DK-A3W135BM16AEA Agilex 3 FPGA and SoC C-Series מספקת פלטפורמה קומפקטית עבור בינה מלאכותית בקצה ממוקדת ביעילות. (מקור תמונה: Altera)

איור 4: ערכת הפיתוח Altera DK-A3W135BM16AEA Agilex 3 FPGA and SoC C-Series מספקת פלטפורמה קומפקטית עבור בינה מלאכותית בקצה ממוקדת ביעילות. (מקור תמונה: Altera)

סיכום

הכניסה של מודלי שפה גדולים (LLMs) ועומסי עבודה חדשים אחרים של בינה מלאכותית בקצה הרשת גורמת למפתחים לחפש גישות חדשות. מערכי FPGA מציעים פתרון ייחודי שמספק לא רק ביצועים דטרמיניסטיים עם השהייה נמוכה, אלא גם מטפל בפונקציות מערכת רבות אחרות. באמצעות רכיבי ה-Agilex FPGA המותאמים ל-AI וחבילת ה-FPGA AI Suite, מפתחים יכולים לגשת ליכולות אלו במהירות ובקלות, מה שפותח אפשרויות ארכיטקטוניות חדשות עבור תכנונים אדפטיביים (סתגלניים) ביותר בעלי אורך חיים ארוכים.

מיאון אחריות: דעות, אמונות ונקודות מבט המובעות על ידי מחברים שונים ו/או משתתפי פורום באתר אינטרנט זה לא בהכרח משקפות את הדעות, האמונות ונקודות המבט של חברת DigiKey או את המדיניות הרשמית של חברת DigiKey.