ארכיטקטורת מעבד-משותף: ארכיטקטורת מערכות משובצות עבור בנייה מהירה של אב-טיפוס

2021-07-06

הערת העורך - למרות שהיא ידועה בביצועי ובתפוקת העיבוד הדיגיטלי שלה, ארכיטקטורת מעבד-משותף מעניקה למתכנני מערכות משובצות הזדמנויות לממש אסטרטגיות ניהול פרויקטים המשפרות הן את עלויות הפיתוח והן את זמן היציאה לשוק. מאמר זה, המתמקד ספציפית בשילוב של מיקרו-בקר (MCU) בדיד עם מערך שערים ניתן-לתכנות בשטח (FPGA) בדיד, מציג כיצד ארכיטקטורה זו מתאימה לתהליך תכנון יעיל ואיטרטיבי. תוך מינוף מקורות נחקרים, ממצאים אמפיריים וחקרי מקרים, יתרונות ארכיטקטורה זו נבחנים, ומוצגים יישומים לדוגמא. בסיום מאמר זה, מתכנני מערכות משובצות יבינו טוב יותר מתי ואיך לממש ארכיטקטורת חומרה ורסאטילית זו.

מבוא

מתכנן מערכות משובצות מוצא עצמו בצומת של מגבלות תכנון, ציפיות ביצועים וחששות לוח הזמנים ותקציב. ואכן, גם הסתירות בבאזוורדס ובביטויים מודרניים של ניהול פרויקטים מדגישות עוד יותר את האופי המסוכן של תפקיד זה: "להיכשל מהר"; "להיות זריז"; "להיות מובטח-עתיד"; ו"להיות משבש! ". האקרובטיקה הכרוכה אפילו בניסיון לספק ציפיות אלו יכולה להיות כואבת, ובכל זאת, הדברים נאמרים וממשיכים להתחזק בכל השוק. מה שנדרש הוא גישת תכנון המאפשרת ליישם תהליך איטרטיבי אבולוציוני, וכמו ברוב המערכות המשובצות, זה מתחיל בארכיטקטורת החומרה.

ארכיטקטורת מעבד-משותף, ארכיטקטורת חומרה הידועה בשילוב נקודות החוזק של מיקרו-בקר (MCU) וטכנולוגיות מערך שערים ניתן-לתכנות בשטח (FPGA), יכולה להציע למתכנן מערכות משובצות תהליך המסוגל לעמוד אפילו בדרישות התובעניות ביותר, ועדיין מאפשר את הגמישות הדרושה כדי להתמודד עם אתגרים ידועים ולא-ידועים כאחד. הודות לאספקת חומרה המסוגלת להתאים איטרטיבית, המתכנן יכול להציג התקדמות, להשיג את אבני-הדרך הקריטיות ולנצל באופן מלא את תהליך הבנייה המהירה של אב-טיפוס.

בתוך תהליך זה ישנן אבני-דרך עיקריות בפרויקט שלכל אחת מהן ערך ייחודי משלהן המוסיף למאמץ הפיתוח. במאמר זה נתייחס אליהן באמצעות המונחים הבאים: אבן-הדרך של עיבוד אותות דיגיטלי עם מיקרו-בקר, אבן-הדרך של ניהול מערכת עם מיקרו-בקר ואבן-הדרך של פרישת המוצר.

בסיום מאמר זה יוכח כי ארכיטקטורת חומרה גמישה יכולה להתאים טוב יותר לתכנון מערכות משובצות מודרניות לעומת גישה קשיחה יותר. יתר על כן, גישה זו יכולה לגרום לשיפור הן בעלות הפרויקט והן בזמןהיציאה לשוק. טיעונים, דוגמאות וחקרי מקרים ישמשו להגנה על עמדה זו. על ידי התבוננות בערך של כל אבן-דרך בתוך גמישות התכנון שמספקת ארכיטקטורה זו, מתברר כי ארכיטקטורת חומרה אדפטיבית היא מניע רב-עוצמה בדחיפה קדימה של תכנון מערכות משובצות.

בחינת נקודות החוזק של ארכיטקטורת מעבד-משותף: גמישות תכנון ועיבוד עם ביצועים עיליים

יישום נפוץ עבור תכני FPGA הוא ממשק ישיר לממיר אנלוגי-לדיגיטלי (ADC) במהירות גבוהה. האות עובר דיגיטיזציה, נקרא לתוך ה- FPGA, ואז כמה אלגוריתמים של עיבוד אותות דיגיטלי (DSP) מיושמים על אות זה. לבסוף, ה- FPGA מקבל החלטות על סמך הממצאים.

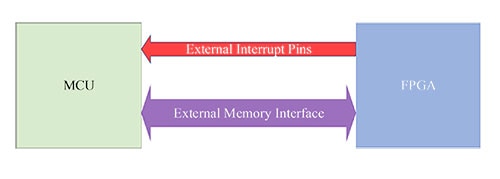

יישום כזה ישמש כדוגמה במאמר זה. יתר על כן, איור 1 ממחיש ארכיטקטורה כללית של מעבד-משותף, כאשר ה- MCU ו- FPGA מחוברים דרך ממשק הזיכרון החיצוני של המיקרו-בקר. ה- FPGA מטופל כאילו מדובר ביחידת זיכרון גישה אקראית סטטי (SRAM) חיצוני. האותות המגיעים חזרה ל- MCU מה- FPGA ומשמשים כקווי פסק (Interrupt) ומחווני סטטוס בחומרה. זה מאפשר ל- FPGA לציין מצבים קריטיים ל- MCU, כגון הודעה שהמרת ה- ADC מוכנה, או שארעה תקלה, או שהתרחש אירוע ראוי לציון אחר.

איור 1: תרשים של מעבד-משותף גנרי (MCU + FPGA). (מקור התמונה: CEPD)

איור 1: תרשים של מעבד-משותף גנרי (MCU + FPGA). (מקור התמונה: CEPD)

נקודות החוזק של גישת המעבד-המשותף ניכרות ככל הנראה בצורה הטובה ביותר בתפוקות של כל אחת מאבני-הדרך שהוזכרו לעיל. ההערכה היא לא רק בעצם רשימת ההישגים של כל משימה או שלב, אלא גם בהשפעות של הישגים אלו על ההמשך. התשובות לשאלות הבאות מסייעות בקביעת הערך הכולל של תפוקות אבני-הדרך:

- האם ההתקדמות של חברי הצוות האחרים יכולה להמשיך מהר יותר, מכיוון שהתלויות וצווארי הבקבוק בפרויקט מוסרים?

- כיצד הישגי אבן-הדרך מאפשרים מסלולי ביצוע מקבילים נוספים?

אבן-הדרך של עיבוד אותות דיגיטלי עם המיקרו-בקר

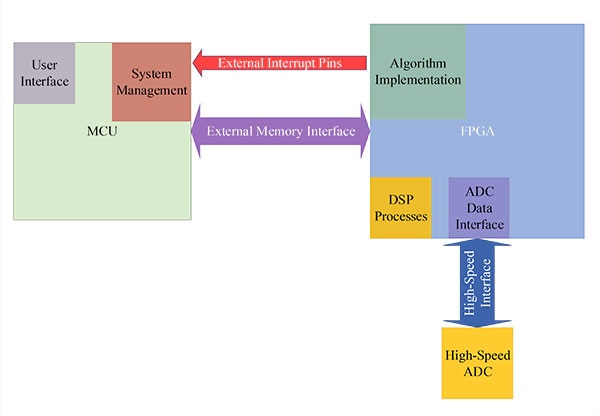

איור 2: תרשים ארכיטקטורת עיבוד אותות דיגיטלי עם המיקרו-בקר. (מקור התמונה: CEPD)

איור 2: תרשים ארכיטקטורת עיבוד אותות דיגיטלי עם המיקרו-בקר. (מקור התמונה: CEPD)

שלב הפיתוח הראשון שארכיטקטורת חומרה זו מאפשרת מציב את ה-MCU כמרכז. כאשר כל הדברים האחרים שווים, פיתוח תוכנה עבור המיקרו-בקר דורש פחות משאבים וזמן לעומת פיתוח FPGA ושפת תיאור חומרה (HDL). לכן, באמצעות פיתוח מוצרים עם ה- MCU כמעבד ראשי, ניתן לממש, לבחון ולאמת אלגוריתמים מהר יותר. זה מאפשר לגלות באגים בלוגיקה ובאלגוריתמים בשלב מוקדם בתהליך התכנון, וזה מאפשר גם לבדוק ולאמת חלקים ניכרים משרשרת האותות.

תפקיד ה- FPGA באבן-דרך ראשונית זו הוא לשמש כממשק איסוף נתונים במהירות גבוהה. המשימה שלו היא הצנרת נתונים אמינה מה- ADC במהירות גבוהה, התרעה ל- MCU שהנתונים זמינים, והצגת נתונים אלה על ממשק הזיכרון החיצוני של ה- MCU. למרות שתפקיד זה אינו כולל מימוש תהליכי DSP מבוססי-HDL או אלגוריתמים אחרים, הוא בכל זאת קריטי ביותר.

פיתוח ה- FPGA המבוצע בשלב זה מניח את הבסיס להצלחה האולטימטיבית של המוצר הן במאמצי פיתוח המוצר והן בהשקתו. הודות להתמקדות בממשק ברמה-נמוכה בלבד, ניתן להקדיש זמן מספק לבדיקת פעולות חיוניות אלה. רק לאחר שה- FPGA מבצע את תפקיד ממשק זה בצורה אמינה ובטוחה, ניתן לסיים אבן-דרך זו בביטחון.

התפוקות העיקריות מאבן-דרך ראשונית זו כוללות את היתרונות הבאים:

- נתיב האותות השלם - כל ההגברות, הניחותים וההמרות - ייבדקו ויאומתו.

- הזמן ומאמץ הפיתוח של הפרויקט יופחתו הודות למימוש ראשוני של אלגוריתמים בתוכנה (++C/C); זהו ערך משמעותי עבור ההנהלה ובעלי העניין האחרים, החייבים לראות את כדאיות הפרויקט לפני שהם מאשרים שלבי תכנון עתידיים.

- הלקחים שנלמדו ממימוש האלגוריתמים ב- ++C/C יועברו ישירות למימושי HDL - באמצעות כלי תוכנה-ל-HDL, לדוגמא HLS מבית Xilinx.

ניהול המערכת עם אבן-הדרך של המיקרו-בקר

איור 3: ארכיטקטורה - ניהול מערכת עם מיקרו-בקר. (מקור התמונה: CEPD)

איור 3: ארכיטקטורה - ניהול מערכת עם מיקרו-בקר. (מקור התמונה: CEPD)

שלב הפיתוח השני, שמציעה גישת מעבד-משותף זו, מוגדר על ידי העברת תהליכי DSP ומימוש אלגוריתמים מה- MCU ל- FPGA. ה- FPGA עדיין אחראי על ממשק ADC במהירות גבוהה, עם זאת, על ידי מימוש תפקידים אחרים אלה, המהירות והמקביליות שמציע ה- FPGA מנוצלים במלואם. בנוסף, בניגוד ל- MCU, ניתן לממש מספר מופעים של תהליכי DSP וערוצי אלגוריתם, ולהריץ אותם בו-זמנית.

בונה על השיעור שנלמד ממימוש ה- MCU, המתכנן מעביר ביטחון זה לתוך אבן-דרך הבאה זו. כלים, כגון Vivado HLS מבית Xilinx שהוזכר לעיל, מספקים תרגום פונקציונלי מקוד ++C/C הניתן-להרצה ל- HDL ניתן -לסינתזה. כעת, עדיין יש להגדיר ולממש מגבלות תזמון, פרמטרי תהליכים והעדפות משתמש אחרות, אולם פונקציונליות הליבה נשמרת ומתורגמת למארג ה- FPGA.

עבור אבן-דרך זו, תפקיד ה- MCU הוא של מנהל מערכת. אוגרי סטטוס ובקרה בתוך ה- FPGA מנוטרים, מעודכנים ומדווחים על ידי ה- MCU. יתר על כן, ה- MCU מנהל את ממשק המשתמש (UI). ממשק משתמש זה יכול ללבוש את צורתו של שרת אינטרנט אליו ניגשים דרך חיבור Ethernet או Wi-Fi, או שהוא יכול להיות ממשק עם מסך מגע תעשייתי הנותן גישה למשתמשים בנקודת השימוש. הלקח העיקרי מתפקידו החדש והמעודן יותר של ה- MCU הוא זה: על ידי הקלת משימות העיבוד העתיר-חישובים, הן ה- MCU והן ה- FPGA ממונפים כעת במשימות עבורן הם מתאימים היטב.

התפוקות העיקריות מאבן-דרך זו כוללות את היתרונות הבאים:

- ביצוע מהיר ומקבילי של תהליכי DSP ומימוש אלגוריתמים המבוצע על ידי ה- FPGA.ה- MCU מספק ממשק משתמש מגיב ויעיל ומנהל את תהליכי המוצר.

- לאחר שפותח ואומת לראשונה בתוך ה- MCU, סיכוני האלגוריתמים הוקלו, והקלות אלו מתורגמות לתוך HDL ניתן-לסינתזה. כלים, כגון Vivado HLS, הופכים את תרגום זה לתהליך קל יותר. יתר על כן, ניתן להקל סיכונים ספציפיים ל- FPGA באמצעות כלי סימולציה משולבים, כגון חבילת התכנון Vivado.

- בעלי העניין אינם חשופים לסיכון משמעותי עקב העברת התהליכים ל- FPGA. להפך, הם זוכים לראות וליהנות מהיתרונות שמספקות המהירות והמקביליות של ה- FPGA. ניתן לצפות בשיפורי ביצועים ניתנים-למדידה, וכעת ניתן להתמקד בהכנת תכן זה עבור הייצור.

אבן-הדרך של פרישת המוצר

עם העיבוד העתיר-חישובים המטופל בתוך ה- FPGA, וה- MCU המטפל בתפקידיו בניהול המערכת וממשק המשתמש, המוצר מוכן לפרישה. מאמר זה אינו תומך בעקיפת מהדורות אלפא ובטא; עם זאת, הדגש עבור אבן-דרך זו הוא היכולות שארכיטקטורת המעבד המשותף מספקת לפרישת מוצרים.

הן ה- MCU והן ה- FPGA הם התקנים הניתנים לעדכון בשטח. מספר פיתוחים נעשו כדי שעדכוני FPGA יהיו נגישים בדיוק כמו עדכוני תוכנה. יתר על כן, מכיוון שה- FPGA נמצא בתוך מרחב הזיכרון הניתן לגישה לפי כתובת של ה- MCU, ה- MCU יכול לשמש כנקודת הגישה של המערכת כולה: קבלת שני העדכונים, עבור עצמו כמו גם עבור ה- FPGA. ניתן לתזמן עדכונים לפי תנאים, להפיץ ולהתאים במיוחד לכל משתמש קצה בנפרד. ולבסוף, ניתן לשמור על רשומות משתמשים ומקרי שימוש ולשייך אותם למימושי בנייה ספציפיים. ממערכי נתונים אלה ניתן להמשיך ולשפר את הביצועים גם לאחר שהמוצר נמצא כבר בשטח.

נקודות החוזק של יכולת-עדכון מערכת-כוללת זו מודגשות אולי במיוחד ביישומים מבוססי-חלל. לאחר השקת המוצר, חייבים לבצע תחזוקה ועדכונים מרחוק. זה עשוי להיות פשוט כמו שינוי תנאים לוגיים, או מסובך כמו עדכון שיטת אפנון תקשורת. יכולת התכנות המוצעת על ידי טכנולוגיות FPGA וארכיטקטורת מעבד-משותף עשויה להקיף את מכלול היכולות הללו, הכול עם היצע של מבחר רכיבים מוקשחי-קרינה.

הלקח האחרון מאבן-דרך זו הוא הפחתת עלויות פרוגרסיבית. הפחתת עלויות, שינויים במפרט החומרים (BOM) ואופטימיזציות אחרות יכולות להתרחש גם באבן-דרך זו. במהלך הפרישות בשטח, יתכן ויתברר שהמוצר יכול לפעול באותה מידה עם MCU יקר פחות כמו גם FPGA בעל יכולת פחותה. הודות לארכיטקטורת מעבד-משותף, המתכננים אינם תקועים עם רכיבים שהיכולות שלהם חורגות מצורכי היישום. יתר על כן, במידה ורכיב אינו זמין, הארכיטקטורה מאפשרת שילוב רכיבים חדשים בתכן. זה לא המקרה עם שבב יחיד, מערכת-על-שבב (SoC), או עם DSP או MCU עם ביצועים עיליים המנסים לטפל בכל העיבודים במוצר. ארכיטקטורת המעבד-המשותף היא שילוב טוב של יכולת וגמישות המעניקה למתכנן יותר אפשרויות בחירה ודרגות חופש בשלבי הפיתוח ועם היציאה לשוק.

תמיכה במחקר ובחקרי מקרים קשורים

דוגמה של תקשורת לוויינים

בקיצור, הערך של מעבד-משותף הוא בהורדת העומס מיחידת העיבוד הראשית כך שמשימות מבוצעות בחומרה, בה ניתן לנצל את היתרונות של מאיצים. היתרון בבחירת תכן כזה הוא שיפור נטו במהירות ויכולות החישוב, וכפי שטוען מאמר זה, הפחתה בעלות הפיתוח וקיצור זמן הפיתוח. אחד התחומים שהוא אולי מהמשכנעים ביותר ליתרונות אלה הוא תחום מערכות תקשורת חלל.

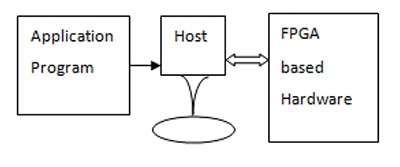

במאמרם חומרה מבוססת FPGA כמעבד, G. Prasad ו- N. Vasantha מפרטים כיצד עיבוד נתונים בתוך FPGA משלב את הצרכים החישוביים של מערכות תקשורת לווינים ללא עלויות הנדסה חד-פעמיות (NRE) הגבוהות של מעגלים משולבים ספציפיים-ליישום ( ASIC) או המגבלות הספציפיות-ליישום של מעבד ארכיטקטורה קשיחה. בדיוק כפי שתואר באבן-דרך של עיבוד אותות דיגיטלי עם מיקרו-בקר, התכנון שלהם מתחיל בכך שמעבד היישום מבצע את מרבית האלגוריתמים עתירי-חישובים. מנקודת התחלה זו, הם מזהים את מקטעי המפתח של התוכנה הצורכים את מרבית מחזורי שעון יחידת העיבוד המרכזית (CPU) ומעבירים את המקטעים הללו למימוש HDL. הייצוג הגרפי דומה מאוד למה שהוצג עד כה, אולם הם בחרו לייצג את תוכנית היישום כבלוק עצמאי, מכיוון שניתן לממש אותו במארח (מעבד) או בחומרה מבוססת FPGA.

איור 4: תוכנית יישום, מעבד מארח וחומרה מבוססת-FPGA המשמשים בדוגמא של תקשורת לוויינים.

איור 4: תוכנית יישום, מעבד מארח וחומרה מבוססת-FPGA המשמשים בדוגמא של תקשורת לוויינים.

הודות לשימוש בממשק חיברור רכיבים היקפיים (PCI) וגישה ישירה לזיכרון (DMA) של המעבד המארח, ביצועי הרכיבים ההיקפיים משופרים דרמטית. השיפורים בולטים בעיקר עבור תהליך ה- Derandomization. כאשר תהליך זה בוצע בתוכנה של המעבד המארח, היה בבירור צוואר בקבוק בהיענות בזמן-אמת של המערכת. עם זאת, כשעברו ל- FPGA נצפו היתרונות הבאים:

- תהליך ה-Derandomization מבוצע בזמן-אמת מבלי לגרום לצווארי בקבוק

- תקורת החישוב של המעבד המארח צומצמה משמעותית, וכעת היא יכולה לבצע טוב יותר את תפקיד הרישום הרצוי.

- הביצועים הכוללים של המערכת כולה הוגדלו.

כל זה הושג ללא העלויות הכרוכות ב- ASIC, ותוך כדי ניצול הגמישות של הלוגיקה הניתנת-לתכנות [5]. תקשורת לווינים מציבה אתגרים ניכרים, וניתן לאמת גישה זו לעמידה בדרישות, ועדיין להמשיך להעניק גמישות תכנון.

הדוגמא של מערכות מידע ובידור לכלי-רכב

מערכות בידור בתוך רכבים מהוות מאפיין מבדל עבור צרכנים חדי-עין. בניגוד לרוב מוצרי האלקטרוניקה לכלי-רכב, התקנים אלו הם נראים לעין ואמורים לספק זמן תגובה וביצועים יוצאי-דופן. עם זאת, לעתים המתכננים נלחצים בין צורכי התכן הנוכחיים לבין הגמישות שתידרש עבור מאפיינים עתידיים. עבור דוגמא זו, צורכי המימוש של עיבוד אותות ותקשורת אלחוטית ישמשו כדי להדגיש את נקודות החוזק של ארכיטקטורת החומרה של המעבד-המשותף.

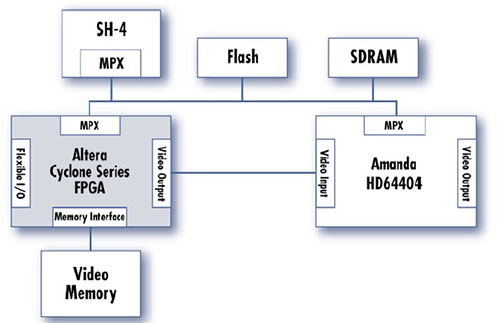

אחת מהארכיטקטורות הבולטות של מערכות בידור לכלי-רכב בהן השתמשו פורסמה על ידי תאגיד Delphi Delco Electronics Systems. בארכיטקטורה זו השתמשו ב- SHU-4 MCU עם ASIC נלווה, הרכיב ההיקפי HD64404 Amanda מבית Hitachi. ארכיטקטורה זו סיפקה למעלה מ- 75% מפונקציונליות הבידור הבסיסית של שוק הרכב; עם זאת, היא חסרה את היכולת לטפל ביישומי עיבוד וידאו ותקשורת אלחוטית. הודות להכללת FPGA בארכיטקטורה קיימת זו, ניתן להוסיף גמישות ויכולת נוספות לגישת תכן שכבר-קיים זה.

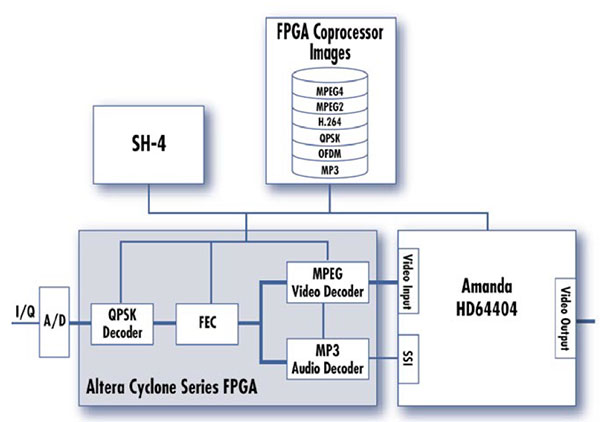

איור 5: דוגמא 1 של ארכיטקטורת מעבד-משותף עם FPGA עבור מערכות מידע ובידור.

איור 5: דוגמא 1 של ארכיטקטורת מעבד-משותף עם FPGA עבור מערכות מידע ובידור.

הארכיטקטורה באיור 5 מתאימה הן לעיבוד וידאו והן לניהול תקשורת אלחוטית. הודות להעברת פונקציות ה- DSP ל- FPGA, מעבד Amanda יכול לשמש לתפקיד של ניהול מערכת והוא חופשי לממש חבילת תוכנה של תקשורת אלחוטית. מכיוון שגם לAmanda וגם ל- FPGA יש גישה לזיכרון החיצוני, ניתן להחליף נתונים במהירות בין מעבדי המערכת ורכיביה.

איור 6: דוגמא 2 של ארכיטקטורת מעבד-משותף עם FPGA עבור מערכות מידע ובידור.

איור 6: דוגמא 2 של ארכיטקטורת מעבד-משותף עם FPGA עבור מערכות מידע ובידור.

מערכת מידע ובידור השנייה שבאיור 6 מדגישה את יכולתו של ה- FPGA לטפל הן בנתונים האנלוגיים במהירות גבוהה הנכנסים והן בטיפול בדחיסה ובקידוד הדרושים עבור יישומי וידאו. למעשה, ניתן להעביר את כל הפונקציונליות הזו אל ה- FPGA, ובאמצעות עיבוד מקבילי ניתן לטפל בכול בזמן-אמת.

הודות להכללת ה- FPGA בארכיטקטורת חומרה קיימת, ניתן לשלב את הביצועים המוכחים של החומרה הקיימת עם גמישות וחסינות-לעתיד. אפילו במערכות קיימות, ארכיטקטורת המעבד-המשותף מעניקה אפשרויות למתכננים שאחרת לא היו קיימות [6].

יתרונות בנייה מהירה של אב-טיפוס

בעיקרו, תהליך בנייה מהירה של אב-טיפוס שואף לכסות כמות משמעותית של תחום פיתוח המוצרים על ידי ביצוע משימות במקביל, זיהוי "באגים" ובעיות תכנון במהירות, ואימות נתונים ומסלולי אותות, במיוחד אלה הנמצאים במסלול הקריטי של הפרויקט. עם זאת, כדי שתהליך זה יניב תוצאות יעילות וביעילות, חייבת להיות מומחיות מספקת בתחומי הפרויקט הנדרשים.

מסורתית, פירוש הדבר הוא שחייבים שיהיו מהנדס חומרה, מהנדס תוכנה משובצת או מהנדס DSP ומהנדס HDL. אמנם יש הרבה אנשי מקצוע בין-תחומיים העשויים להיות מסוגלים למלא מספר תפקידים; עם זאת, עדיין קיימת תקורה משמעותית של הפרויקט בתיאום מאמצים אלה.

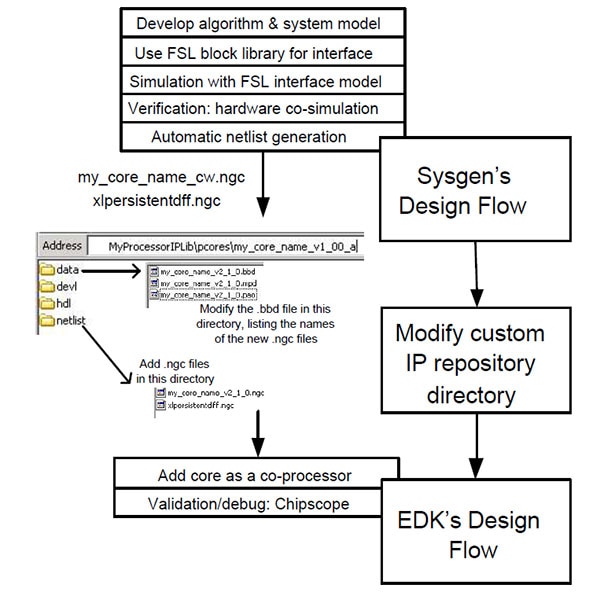

במאמרם פלטפורמת בנייה מהירה של אב-טיפוס מבוססת FPGA עבור מעבדים-משותפים Wavelet, הכותבים מקדמים את הרעיון ששימוש בארכיטקטורת מעבד-משותף מאפשר למהנדס DSP יחיד למלא את כל התפקידים הללו, ביעילות. לצורך מחקר זה, הצוות החל לתכנן ולדמות את פונקציונליות ה- DSP הרצויה בכלי Simulink מבית MATLAB. זה שימש שתי פונקציות עיקריות, בכך שהוא, 1) אימת את הביצועים הרצויים באמצעות סימולציה, ו- 2) שימש קו-בסיס אליו ניתן להשוות ולהתייחס בבחירות תכנון עתידיות.

לאחר סימולציה זוהו פונקציות קריטיות וחולקו לליבות שונות - אלו הם רכיבים ומעבדים עם ליהב רכה שניתן לסנתז בתוך FPGA. השלב החשוב ביותר במהלך עבודה זו היה הגדרת הממשק בין ליבות ורכיבים אלה והשוואת ביצועי החלפת-הנתונים מול ביצועי הסימולציה ואלו הרצויים. תהליך תכנון זה מתואם באופן הדוק עם תזרים תכנון של Xilinx עבור מערכות משובצות והוא מסוכם באיור 7 להלן.

איור 7: תזרים תכנון של המימוש.

איור 7: תזרים תכנון של המימוש.

הודות לחלוקת המערכת לליבות ניתנות-לסינתזה, מהנדסי ה- DSP יכולים להתמקד בהיבטים הקריטיים ביותר בשרשרת עיבוד האותות. הם לא צריכים להיות מומחים בחומרה או HDL כדי לשנות, לנתב או למממש מעבדים או רכיבים שונים של מעבדי הליבה-הרכה שבתוך ה- FPGA. כל עוד המתכננים מודעים לממשק ולפורמטי הנתונים, יש להם שליטה מלאה על מסלולי האותות והם יכולים לשפר את ביצועי המערכת.

ממצאים אמפיריים - חקר המקרה של טרנספורמציית קוסינוס בדידה

הממצאים האמפיריים לא רק אישרו את הגמישות שהעניקה ארכיטקטורת המעבד-המשותף למתכנני המערכות המשובצות, אלא גם הציגו את האפשרויות לשיפור הביצועים הקיימים עם כלי FPGA מודרניים. שיפורים, כמו אלה המוזכרים להלן, עשויים שלא להיות זמינים או עשויים להשפיע פחות על ארכיטקטורות חומרה אחרות. טרנספורמציית קוסינוס בדידה (DCT) נבחרה כאלגוריתם עתיר-חישובים, וההעברה שלה ממימוש מבוסס-C למימוש מבוסס-HDL עמדה במרכז ממצאים אלה. ה- DCT נבחר מאחר ואלגוריתם זה משמש בעיבוד אותות דיגיטלי לצורך זיהוי וסינון תבניות [8]. הממצאים האמפיריים התבססו על תרגיל מעבדה שהושלם על ידי הכותב ועמיתים-לעבודה כדי להשיג את הרשאת Xilinx Alliance Partner לשנים 2020-2021.

הכלים וההתקנים הבאים שימשו עבור מאמצים אלו:

- Vivado HLS גרסת 2019

- ההתקן עבור הערכה וסימולציה היה ה- xczu7ev-ffvc1156-2-e

החל מהמימוש מבוסס -C, אלגוריתם DCT מקבל שני מערכים של מספרים של Bit-16; מערך "a" הוא מערך הכניסה ל- DCT, ומערך "b" הוא מערך היציאה מה- DCT. רוחב הנתונים (DW) מוגדר אפוא כ- 16 ומספר האלמנטים (N) בתוך המערכים הוא DW/1024, או 64. ולבסוף, הגודל של מטריצת DCT (DCT_SIZE) מוגדר ל- 8, כלומר משתמשים במטריצה של 8 x 8.

בהמשך להנחת היסוד של מאמר זה, מימוש האלגוריתם מבוסס-C מאפשר למתכננים לפתח ולאמת במהירות את פונקציונליות האלגוריתם. למרות שהוא שיקול חשוב, אימות זה מציב פונקציונליות בשקלול גבוה יותר מאשר זמן הביצוע. שקלול זה מותר מאחר והמימוש האולטימטיבי של אלגוריתם זה יהיה ב- FPGA, שבו קיימות האצה בחומרה, טרנספורמציית חוג וטכניקות אחרות.

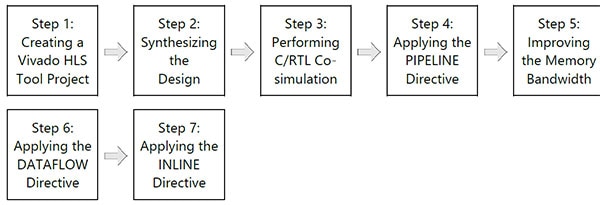

איור 8: תזרים תכנון HLS עם Vivado מבית Xilinx.

איור 8: תזרים תכנון HLS עם Vivado מבית Xilinx.

לאחר יצירת קוד ה- DCT בכלי Vivado HLS כפרויקט, השלב הבא הוא להתחיל לסנתז את התכן עבור מימוש ב- FPGA. בדיוק בשלב הבא הזה ניכרים עוד יותר היתרונות המשפיעים ביותר מהעברת ביצוע אלגוריתם מה- MCU ל- FPGA - שלב זה אקוויוולנטי, כייחוס, לניהול המערכת עם אבן-הדרך של המיקרו-בקר שנידון לעיל.

כלי FPGA מודרניים מאפשרים חבילת אופטימיזציות המשפרות מאוד את הביצועים של אלגוריתמים מורכבים. לפני ניתוח התוצאות, יש לשים לב לכמה מונחים חשובים:

- שיהוי (Latency) - מספר מחזורי השעון הנדרשים לביצוע כל איטרציות החוג [10]

- אינטרוול - מספר מחזורי השעון לפני שהאיטרציה הבאה של החוג מתחילה לעבד נתונים [11]

- BRAM - Block Random Access Memory

- DSP48E - פרוסת עיבוד אותות דיגיטלי עבור ארכיטקטורת ה- UltraScale

- FF - Flip-Flop

- LUT - Look-up Table

- URAM - Unified Random-Access Memory (יכול להיות מורכב מטרנזיסטור יחיד)

|

||||||||||||||||||||||||||||||||||||||||

טבלה 1: ממצאי האופטימיזציה של ביצוע אלגוריתם FPGA (שיהוי ואינטרוול).

|

טבלה 2: ממצאי האופטימיזציה של ביצוע באלגוריתם ב- FPGA (ניצול המשאבים).

ברירת-המחדל

הגדרות ברירת-המחדל לאופטימיזציה מגיעות מהתוצאות ללא-שינוי של תרגום האלגוריתם מבוסס-C ל- HDL ניתן-לסינתזה. אופטימיזציות אינן מאופשרות, וזה יכול לשמש כייחוס ביצועים כדי להבין טוב יותר את האופטימיזציות האחרות.

חוג הצנרה פנימי

הנחיית PIPELINE מורה ל- Vivado HLS לפתוח את החוגים הפנימיים כך שניתן יהיה לעבד נתונים חדשים בזמן שהנתונים הקיימים עדיין נמצאים בצינור. כך, נתונים חדשים לא צריכים לחכות שעיבוד הנתונים הקיימים יושלם לפני התחלת העיבוד שלהם.

חוג הצנרה חיצוני

על ידי הפעלת הנחיית PIPELINE על החוג החיצוני, פעולותיו מוצנרות כעת. עם זאת, פעולות החוגים הפנימיים מתרחשות כעת במקביל. זמני השיהוי כמו גם האינטרוול מתקצרים בחצי הודות ליישומם ישירות לחוג החיצוני.

חלוקת המערך

הנחיה זו ממפה את תוכן החוגים למערכים ובכך משטחת את כל הגישות לזיכרון לאלמנטים בודדים בתוך מערכים אלה. על ידי כך נצרך אמנם יותר זיכרון RAM, אך שוב, זמן הביצוע של אלגוריתם זה מתקצר בחצי.

תזרים נתונים

הנחיה זו מאפשרת למתכננים להגדיר את מספר היעד של מחזורי השעון בין כל קריאות הכניסה. הנחיה זו נתמכת רק בפונקציה ברמה-העליונה. רק החוגים והפונקציות נחשפות לרמה זו ייהנו מהנחיה זו.

בקו-אחד

הנחיית INLINE משטחת את כל החוגים, פנימיים וחיצוניים כאחד. תהליכי שורות כמו גם עמודות יכולים כעת להתבצע בו-זמנית. מספר מחזורי השעון הנדרשים הוא במינימום, גם אם הדבר צורך יותר משאבי FPGA.

סיכום

ארכיטקטורת החומרה של מעבד-משותף מספקת למתכנני רכיבים משובצים פלטפורמה עם ביצועים עיליים השומרת על גמישות התכנון שלה בזמן הפיתוח כמו גם אחרי השקת המוצר. הודות לתיקוף האלגוריתמים ב- ++C או C תחילה, תהליכים, מסלולי אותות ונתונים, ופונקציונליות קריטית מאומתים בתוך זמן קצר יחסית. אחר כך, הודות לתרגום האלגוריתמים עתירי-העיבוד למעבד-המשותף FPGA, המתכננים יכולים ליהנות מהיתרונות של האצה בחומרה ותכן יותר מודולרי.

אם חלקים יתיישנו או יידרשו אופטימיזציות, אותה ארכיטקטורה יכולה לאפשר שינויים אלה. ניתן לשלב רכיבי MCU ו- FPGA חדשים בתכן, הכול תוך שהממשקים יכולים להישאר כמות שהם. בנוסף, מכיוון שה- MCU ו- FPGA ניתנים לעדכון בשטח, ניתן ליישם שינויים ואופטימיזציות ספציפיים-למשתמש בשטח ומרחוק.

לסיום, ארכיטקטורה זו משלבת את מהירות הפיתוח והזמינות של ה- MCU עם הביצועים ויכולת ההרחבה של ה- FPGA. עם אופטימיזציות ושיפורי ביצועים הזמינים בכל שלב בפיתוח, ארכיטקטורת המעבד-המשותף יכולה לענות על הצרכים של הדרישות המאתגרות ביותר - הן בתכנים של ימינו והן של העתיד.

מיאון אחריות: דעות, אמונות ונקודות מבט המובעות על ידי מחברים שונים ו/או משתתפי פורום באתר אינטרנט זה לא בהכרח משקפות את הדעות, האמונות ונקודות המבט של חברת DigiKey או את המדיניות הרשמית של חברת DigiKey.