כיצד לאזן ביעילות שיהוי (Latency), רוחב-פס וביצועים עבור פתרונות בדיקה ומדידה

באדיבות ‎DigiKey's North American Editors

2022-11-16

מתכננים של פתרונות בדיקה ומדידה, כגון מיטות מבחן (test beds) ותת-מערכות hardware-in-the-loop (HIL), מאותגרים יותר ויותר למצוא את האיזון אופטימלי של ביצועים עיליים עם שיהוי (Latency) נמוך יותר ורוחב-פס רחב יותר. במקביל, הם חייבים גמישות ויכולת הגדרת-תצורה מחדש כדי לתמוך בדרישות מערכת המשתנות במהירות ולשרת מקרי שימוש רבים.

באופן מסורתי, עמידה בדרישות אלו—תוך כדי שמירה על ביצועי AC ו-DC מדויקים כשקצבי דגימה גדלים—דורשת זמן תכנון/ניפוי-שגיאות ומאמץ משמעותיים. מאמץ זה גדל עם כל תכנון-מחדש כשמחליפים רכיבים כדי להתאים לשינויים במיטת מבחן (test bed) ומטרות מכשור.

חלופה טובה יותר היא גישת פלטפורמה המבוססת על התקנים ניתנים-לתכנות, ניתנים להגדרת-תצורה מחדש ולשימוש חוזר. חלקי “עוגן” אלה מכוננים קו בסיס של ביצועים שניתן להשתמש בו—ולהשתמש בו שוב—לרוחב שינויים של יישום מסוג אחד או אפילו יישומים מרובים שונים במהותם.

מאמר זה מציג את הממיר הדיגיטלי-לאנלוגי (DAC) Analog Devices AD3552R כדוגמה לאופן בו רכיבים ניתנים-לתכנות יכולים לממש מטרות של מתכננים ליצור פלטפורמת שרשרת-אותות ניתנת להגדרת-תצורה מחדש, ממוטבת בקלות וניתנת למדרוג. הדיון כולל לוחות הערכה ותמיכת LTspice, כדי לסייע למתכננים בצעדים הראשונים. כמו כן מוצג הממיר האנלוגי-לדיגיטלי (ADC) המשולב במידה רבה ADAQ23878, שביחד עם ה-AD3552R יכולים ליצור שני חלקי עוגן קריטיים משלימים לגישה מבוססת-פלטפורמה.

אינטגרציה ויכולת-תכנות מפשטות תכנים

כשדרישות מערכת בדיקה משתנות, הטכניקות המסורתיות והמצליחות בדרך כלל שמשתמשים בהן למקסום דיוק ולצמצום שגיאות, אפילו אם מדובר בתוספת תכנון ועלות רכיבים, הן:

- בחירת רכיבים “טובים יותר” כמו נגדים עם טולרנס צר יותר או מקדם טמפרטורה נמוך יותר כדי לצמצם ליקוים בביצועים ראשוניים כמו גם לאורך זמן, ועם שינויים בטמפרטורה.

- שימוש בטופולוגיות התומכות במידה רבה בביטול-עצמי של שגיאות בלתי נמנעות, כמו נגדים מותאמים ומעגלים הפרשיים או גשר ה-Wheatstone הקלאסי.

- אספקת כיול ראשוני ומתמשך באמצעות השימוש ברכיב “זהב”, כמו ייחוס מתח מדויק אליו ניתן להשוות את כל המתחים החשובים האחרים.

הצלחת השימוש בטכניקות אלו הופכת להיות מאתגרת יותר עבור מתכנני מערכת בדיקה כשהיישום דורש קצבי עדכון גבוהים עבור ה-ADC וה-DAC.

כדי למנוע רבים מהאתגרים האלה, גישה מבוססת-פלטפורמה ניתנת-לתכנות מציעה אופציה טובה יותר על ידי צמצום—או אפילו ביטול—הצורך לתכנן “מאפס” עבור הפרויקט הראשוני, וכשדרישות משתנות. הגישה גם מבטיחה אמצעי עקבי של סימולציה והערכת תכן. אלמנט קריטי של גישה ניתנת-לתכנות זו הוא ה-DAC (איור 1).

איור 1: המרת DAC היא פונקציה עיקרית ביישומי בדיקה ומכשור; היכולות שלה נמצאות תחת בחינה מדוקדקת ככל שהדרישות ממערכת בדיקה הופכות למאתגרות יותר. (מקור תמונה: Analog Devices)

איור 1: המרת DAC היא פונקציה עיקרית ביישומי בדיקה ומכשור; היכולות שלה נמצאות תחת בחינה מדוקדקת ככל שהדרישות ממערכת בדיקה הופכות למאתגרות יותר. (מקור תמונה: Analog Devices)

יכולות וביצועי ממיר DAC "נלחצים" יותר ויותר על ידי יישומי בדיקה-ובקרה הדורשים דיוק כמו גם מהירות גבוהה בתחום רחב. הם גם דורשים גמישות וחייבים להיות ניתנים להגדרת-תצורה מחדש בקלות מבלי לעבור תכנון מחדש מורכב או מלא, ומחזור הסמכה מחדש.

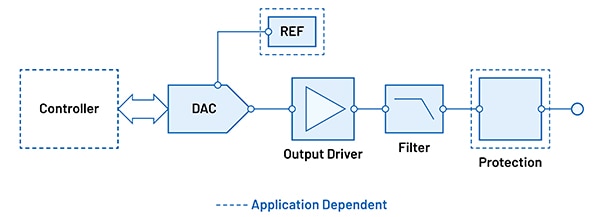

ה-ADI AD3552R יכול להתמודד עם יעדי ביצועים כיוון שהוא ממיר SPI DAC שתי-יציאות, מרובה-תחומים, Bit-16, 33 מיליון עדכונים לשנייה (MUPS) (איור 2). בנוסף לתכונות ביצועים בסיסיות, יתרון נוסף של ה-AD3552R הוא הקלות בה ניתן להגדיר את תצורתו מחדש כדי לעמוד ביעדי פרויקט חדשים או משתנים יכולת הגדרת-תצורה מחדש זו כוללת הבטחה שהוא יעמוד ביעדים אלה עם רמת ביטחון גבוהה, ולא לגרום ל"הפתעות" חדשות ובלתי רצויות.

איור 2: ה-AD3552R הוא ממיר SPI DAC שתי-יציאות, מרובה-תחומים, Bit-16, 33 MUPS, שניתן להגדיר-תצורתו מחדש בקלות עבור מאפייני ביצועים שונים. (מקור תמונה: Analog Devices)

איור 2: ה-AD3552R הוא ממיר SPI DAC שתי-יציאות, מרובה-תחומים, Bit-16, 33 MUPS, שניתן להגדיר-תצורתו מחדש בקלות עבור מאפייני ביצועים שונים. (מקור תמונה: Analog Devices)

ה-AD3552R זמין במארז LFCSP 5 מילימטר (מ"מ) × 5 מ"מ ועובד עם מתח ייחוס קבוע של 2.5 וולט, אך ניתן להגדיר את תצורתו באמצעות תוכנה לתחומי מתח יציאה מרובים. הוא גם מאפשר איזון אופטימלי של ביצועים, דיוק, מהירות וגמישות.

ההתקן כולל שלושה נגדי משוב קיזוז-סחיפה לתמיכה במגבר הטרנסמיפדנס (TIA) החיצוני, שממדרג (scales) את מתח היציאה. אוגרי מדרוג היסט (Offset) והגבר מאפשרים יצירת תחומי מרווח יציאה מרובים, כגון 0 עד 2.5 וולט, 0 עד 10 וולט, 5- עד 5+ וולט ו-10- עד 10+ וולט, כמו גם תחומי ביניים מותאמים-במיוחד עם רזולוציה מלאה של 16-bit.

בנוסף, כדי לטפל בדילמה הידועה היטב "מהירות לעומת דיוק", ה-AD3552R DAC יכול לעבוד במצב מהיר עבור מהירות מקסימלית וזמן התיצבות מהירה ביותר, או מצב דיוק עבור עקביות יציאה ודיוק מקסימלי. במצב המהיר, נתוני ממיר ה-DAC נטענים כמילות bit-16, והתוצאה היא ערוץ-יחיד מתעדכן בקצב של 33 MUPS. לעומת זאת, במצב דיוק, נתונים נטענים כמילות bit-24, והתוצאה היא ערוץ-יחיד מתעדכן בקצב של 22 MUPS.

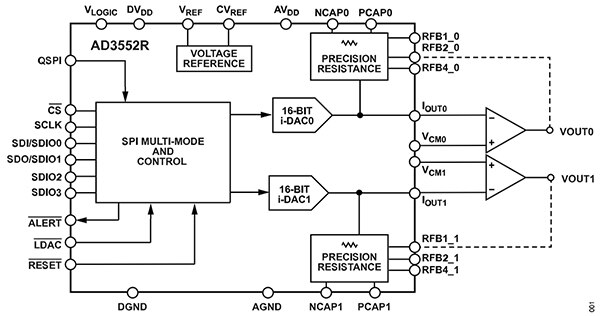

עבור היישומים הדורשים צפיפות רעש נמוכה יותר יחד עם זמן ייצוב מהיר יותר, והיכולים לעבוד עם צריכת הספק גבוהה יותר, ה-AD3552R תומך בשילוב שני ערוצי ה-DAC וביצירת יציאה יחידה (איור 3). שני ממירי ה-DAC חייבים להיות מעודכנים בו-זמנית באותו הקוד כדי לקבל את אותו מתח יציאה המתקבל תוך שימוש ב-DAC יחיד; ה-AD3552R מספק מספר דרכים יעילות לעשות את זה.

איור 3: שתי היציאות של ה-AD3552R ניתנות לשילוב עבור צפיפות רעש נמוכה יותר יחד עם זמן התיצבות מהיר יותר. (מקור תמונה: Analog Devices)

איור 3: שתי היציאות של ה-AD3552R ניתנות לשילוב עבור צפיפות רעש נמוכה יותר יחד עם זמן התיצבות מהיר יותר. (מקור תמונה: Analog Devices)

ישנה גם גמישות בממשק ה-SPI של ההתקן, כיוון שהוא ניתן להגדרה כמצב SPI יחיד (SPI קלאסי), SPI כפול, SPI כפול סינכרוני ו-SPI מרובע (Quad), עם עבודה בקצב נתונים יחיד (SDR) או קצב נתונים כפול (DDR), ועם רמות לוגיות מ-1.2 עד 1.8 וולט. בנוסף, מאחר ושלמות נתונים (data integrity) היא גם כן דאגה גוברת, ניתן לאפשר להתקן לכלול בדיקת יתירות מחזורית (CRC). בודקי שגיאה מרובים שולבו גם כן כדי לגלות כשלי VREF או השחתה של מפת זיכרון.

דגמי סימולציה מאיצים הגדרת תצורה, מחדירים ביטחון

למרות שה-AD3552R הוא התקן מדויק רחב-פס, תמיד יהיו פשרות בין הפרמטרים הרבים הניתנים-לתכנות על-ידי משתמש. כדי להאיץ את ההבנה של ההשפעה של אפשרויות תכנון אלו ולסייע למתכננים בצעדים הראשונים, ההתקן נתמך על ידי לוחות הערכה כמו גם LTspice עבור הערכת רעש, ניתוח טרנזיינטים, סימולציית AC ופרמטרים אחרים. זה מפשט אופטימיזציה של שיהוי (Latency)/ביצועים, כך שמתכננים אינם צריכים לקבוע ערכי פרמטרים או לעשות פשרות ללא נתונים אמינים.

היכולת להשתמש ב-LTspice בשרשרת האותות מביאה את כל האלמנטים שלו יחד כך שמשתמשים יכולים להבין בברור את ביצועים שרשרת האותות השלמים. זה חשוב במיוחד כי ה-AD3552R מציע:

- עשרה תחומי זרם; כתוצאה מהצירוף של ערכי מדרוג הגבר מוגדרים באופן דיגיטלי.

- שלושה ערכי טרנס-אימפדנס-הגבר; כתוצאה מחיבור של אחד מנגדי המשוב.

- סך של 511 ערכי היסט (Offset) DC מוגדרים באופן דיגיטלי.

זה מהווה סך של 15,330 צירופים, בבירור מעבר להקף של כל גישת אב-טיפוס “מעשית” או אפילו הערכה ידנית סלקטיבית.

מודל ה-LTspice עבור ה-AD3552R מעדכן את המודלים של DAC ממוקדי-היציאה-האנלוגית המסורתיים עם סימולציה ממוקדת דיגיטלית יותר. הפונקציונליות של אוגרים מסוימים במודל—במיוחד אלה הקשורים למדרוג הגבר דיגיטלי והיסט (Offset) DC—ניתנים לסימולציה, והמודל יכול לשחזר ביצועים דינמיים ורעש באיכות גבוהה. מבין מאפייני הביצועים של ה-AD3552R שתוכנת ה-LTspice מדמה נמצאים:

- סימולציית תחום יציאה: סימולציית סריקת DC שימושית עבור אישור מרווח מתח היציאה עבור תצורה נתונה של פרמטרים. היא גם מביאה בחשבון את המגבלות הנכפות על ידי מרווח הגובה (החלק העליון של התחום) ומרווח התחתית (תחתית התחום) של מגבר השרת, ובכך קל לצפות כל רוויה של אות היציאה.

- כוונון הענות מדרגה: סימולציית הטרנזיינט עם צורת-גל מדרגה היא שימושית לכוונון הערך של קבל המשוב ומסנן היציאה של ה-TIA כדי להשיג את זמן העלייה המבוקש, זמן ההתייצבות ו-Overshoot, וניתן לשלבה עם סריקת פרמטרים כדי למצוא את הערכים האופטימליים של החלקים. הסימולציה גם מביאה בחשבון את יכולת הדחיפה של המגבר וה-DAC כדי להעריך את קצב השינוי ביציאה (slew rate) וזמן העליה של האות. (שימו לב שערך זה הוא נקודת מוצא כי מעגל הסימולציה אינו כולל את התופעות הפרזיטיות של הלוח והמארזים של החלקים.)

- סימולציית רוחב-פס AC: סימולציית הסריקה AC שימושית לכוונון הערכים של קבל המשוב ומסנן היציאה של ה-TIA ביישומים בהם אות היציאה הוא הרמוני.

- סימולציית צפיפות רעש: זה מאפשר חיזוי של צפיפות הרעש ביציאה של ממיר ה-DAC וה-TIA, שתיהן באזור ה-f/1 ואזור הרעש התרמי. מודל ה-LTspice של ה-AD3552R לוכד את השינוי של צפיפות רעש עם הקוד, וגם מביא בחשבון את ההגבר של ה-TIA, שמגדיל את הרעש ביציאה של DAC הזרם.

למידע נוסף על ה-LTspice, ראה “כיצד להשתמש ב-LTspice כדי לקבוע ביצועי רעש חישה אופטית במהלך תכנון מכשור רגיש.”

תרגל, בדוק, עם חומרה אמיתית

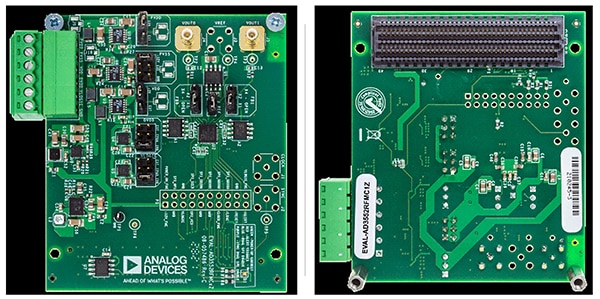

סימולציות הן שימושיות ביותר והכרחיות, אך כפי שכל מהנדס מנוסה יודע, אין הן יכולות להוות תחליף מלא להערכת עולם-אמיתי, במיוחד כשגורמים כגון השפעות פרזיטיות חיצוניות להתקן יכולות להשפיע על הביצועים. עבור ה-AD3552R, צורך זה נענה על ידי שימוש ב-EVAL-AD3552RFMCxZ, שזמין בשני ואריאנטים: ה-EVAL-AD3552RFMC1Z עבור מהירות גבוהה יותר, וה-EVAL-AD3552RFMC2Z עבור דיוק גבוה יותר (איור 4).

איור 4: ה-EVAL-AD3552RFMCxZ (שמאל: שכבה עליונה; ימין: שכבה תחתונה) בא בשתי גרסאות דומות, אחת ממוטבת עבור מהירות והאחרת ממוטבת עבור דיוק. (מקור תמונה: Analog Devices)

איור 4: ה-EVAL-AD3552RFMCxZ (שמאל: שכבה עליונה; ימין: שכבה תחתונה) בא בשתי גרסאות דומות, אחת ממוטבת עבור מהירות והאחרת ממוטבת עבור דיוק. (מקור תמונה: Analog Devices)

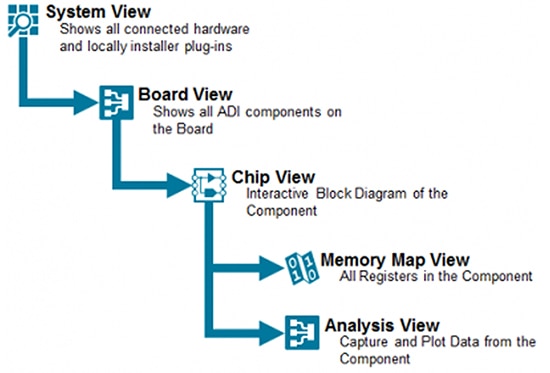

התוכנה עבור הלוח משתמשת בחבילה “Analysis, Control, Evaluation” (ACE) של ADI, יישום שולחני המאפשר את ההערכה והבקרה של מערכות הערכה מרובות לרוחב סל המוצרים של ADI. היישום כולל מסגרת עבודה משותפת ותוכנות נתקעות פרטניות ספציפיות-לרכיב.

עבור ה-AD3552R, ל-ACE יש מספר views לשליטה על היבטים שונים של ה-DAC. כש-view נפתח בפעם הראשונה, הוא יוצר לשונית חדשה בחלק העליון של החלון הראשי. התוכנה הנתקעת AD3552R מייצרת הירארכיה של views: view לוח, view שבב (Chip), view מפת זיכרון ו-view ניתוח המשלב view מחולל צורות גל ו-view מחולל וקטור (איור 5).

איור 5: התוכנה הנתקעת ACE עבור ה-AD3552R מייצרת הירארכיה של views החל מ-view מערכת רמה-גבוהה מטה עד view ניתוח ברמה-בסיסית. (מקור תמונה: Analog Devices)

איור 5: התוכנה הנתקעת ACE עבור ה-AD3552R מייצרת הירארכיה של views החל מ-view מערכת רמה-גבוהה מטה עד view ניתוח ברמה-בסיסית. (מקור תמונה: Analog Devices)

- View הלוח מציג תרשים מפושט של לוח ההערכה, כולל מספר מחברים רלוונטיים והחברור בין שבבים.

- View השבב מציג תרשים פנימי מפושט של השבב ומראה את לוגיקת הממשק, ליבות ממיר ה-DAC, נגדי המשוב המדויקים ואת הפינים הרלוונטיים עבור בלוקים אלה.

- View מפת הזיכרון מציג את כל מרחב התצורה של ה-AD3552R; מרחב זה ניתן להציג כרשימה של אוגרים או כרשימה של שדות ביט.

- View מחולל צורות-הגל מאפשר להקצות וקטורים לערוצים ולהתחיל או להפסיק יצירת צורות גל.

- View מחולל הווקטור מאפשר להגדיר או להעמיס צורות גל שמאוחר יותר ניתן להקצות לערוצי ה-DAC.

תוך שימוש בלוח ההערכה ותוכנת ACE, משתמשים של ה-AD3552R יכולים לאשר את ההחלטות שהם עשו באמצעות סימולטור ה-LTspice ולכוונן לפי הצורך. משתמשים יכולים גם לאמן את ההתקן עם האוגרים, הפונקציות הניתנות-לתכנות והמאפיינים הרבים שלו.

חקור אפשרויות איסוף נתונים אחרות

האפשרויות לרכיבים ניתנים-לתכנות ברמה גבוהה היכולים לשמש ליצירת פלטפורמות שרשרת-אותות ניתנות להגדרת-תצורה מחדש, ממוטבות בקלות וניתנות למדרוג, אינן מוגבלות להתקנים כגון ה-AD3552R.

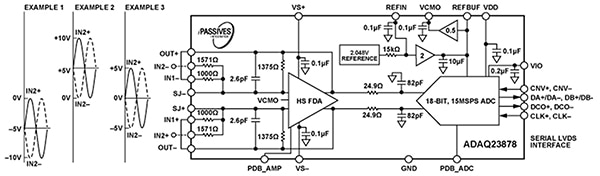

לדוגמה, ה-ADAQ23878 של Analog Devices הוא ADC עם תחום כניסה ניתן לבחירה על ידי פין, 15-MSPS µModule, .18-bit פתרון איסוף-נתונים מהירות-גבוהה זה מפשט ומאיץ את מחזור הפיתוח של מערכות מדידה מדויקות על ידי מניעת חלק גדול מנטל התכנון של בחירת רכיבים, אופטימיזציה ופריסה, באמצעות השימוש בהתקן מוכן-מן-המדף.

על ידי שימוש בטכנולוגיית מערכת-במארז (SIP), ה-ADAQ23878 מקטין את מספר הרכיבים במערכת הסופית על ידי שילוב בלוקים שכיחים מרובים של עיבוד ואכשור אותות בהתקן יחיד. הוא כולל מגבר דוחף ADC רעש-נמוך הפרשי מלא, חוצץ ייחוס (reference buffer) יציב וממיר ADC אוגר קירוב עוקב (SAR) 15 MSPS, 18-bit, מהירות-גבוהה (איור 6).

איור 6: ה-Analog Devices ADAQ23878 משלב בלוקים של עיבוד ואכשור אותות בהתקן יחיד, מקטין למינימום את הצורך ברכיבים חיצוניים. (מקור תמונה: Analog Devices)

איור 6: ה-Analog Devices ADAQ23878 משלב בלוקים של עיבוד ואכשור אותות בהתקן יחיד, מקטין למינימום את הצורך ברכיבים חיצוניים. (מקור תמונה: Analog Devices)

ה-ADAQ23878 גם כולל את הרכיבים הפסיביים הקריטיים עם מאפייני התאמה וסחף מעולים המתקבלים על ידי השימוש בטכנולוגיית iPassive של ADI, שמקטינה למינימום מקורות שגיאה תלויי-טמפרטורה עבור ביצועים אופטימליים. חתימת-השטח הקטנה של 9 מ"מ × 9 מ"מ בלבד, עם 0.8 מ"מ פסיעה ומארז CSP BGA 100-כדוריות, מאפשרת מכשירים בעלי גורם צורה קטן יותר מבלי להקריב ביצועים (איור 7).

איור 7: טכנולוגיית ה-SIP של Analog Devices ADAQ23878 כוללת רכיבים אקטיביים ופסיביים בהתקן קל-ליישום יחיד, תוך אפשור צמצום של מקורות שגיאה קשורות לסחף. (מקור תמונה: Analog Devices)

איור 7: טכנולוגיית ה-SIP של Analog Devices ADAQ23878 כוללת רכיבים אקטיביים ופסיביים בהתקן קל-ליישום יחיד, תוך אפשור צמצום של מקורות שגיאה קשורות לסחף. (מקור תמונה: Analog Devices)

אינטגרציית המערכת פותרת אתגרי תכנון רבים בעוד ההתקן עדיין מספק את הגמישות של חוג משוב דוחף-ADC ניתן להגדרת-תצורה כדי לאפשר התאמות הגבר או הנחתה, כמו גם כניסה הפרשית מלאה או קצה-יחיד (Single-Ended)-להפרשית.

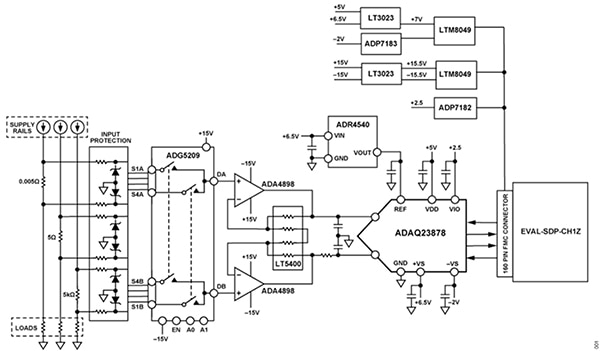

לדוגמה, הוא יכול להוות את הליבה של ציטומטר זרימה שלם (ראה, “ממש במהירות תכני ציטומטר זרימה תוך שימוש במודולים של איסוף נתונים דיוק-גבוה”), או מערכת מדידת זרם תחום-רחב עם ביצועי דיוק, רוחב-פס וסחף ברי השוואה לציוד בדיקה שולחני ומורכב-כונן עבור סביבת בדיקה של ייצור (איור 8). במקביל, הפתרון הוא קטן מספיק כדי להיכלל ביישומים החייבים להיות מנוטרים ברציפות.

איור 8: עם רכיבי תמיכה אקטיביים ופסיביים מתאימים ייחודיים-ליישום, ה-ADAQ23878 מתפקד כליבה של מערכת איסוף נתונים המניבה מדידת זרם מדויקת בתחום דינמי רחב. (מקור תמונה: Analog Devices)

איור 8: עם רכיבי תמיכה אקטיביים ופסיביים מתאימים ייחודיים-ליישום, ה-ADAQ23878 מתפקד כליבה של מערכת איסוף נתונים המניבה מדידת זרם מדויקת בתחום דינמי רחב. (מקור תמונה: Analog Devices)

התכן מתאפיין במדידה בדיוק-גבוה של שלושה תחומי זרם תוך שימוש בשילוב של נגדי מצד (Shunt), מגברים מובנים וה-ADAQ23878 μModule. פתרון זה מגדיל את מספר הערוצים ללוח למרות מגבלות גודל, תוך כדי גם מיתון אתגרים תרמיים, מקל על נטל הכיול של סחף המערכת בשל חימום עצמי וממטב את ביצועי הדיוק הכולל. פריסת הלוח משתמשת בנגדי מצד (Shunt) ארבעה-הדקים עם חיבור Kelvin מובנה המפחיתה השפעות מקדם טמפרטורה של התנגדות (TCR), מציעה יציבות טמפרטורה משופרת בהשוואה לנגדי מצד (Shunt) שני-הדקים (איור 9).

איור 9: המערכת השלמה למדידת זרם המבוססת על ה-ADAQ23878 μModule היא קטנה יותר מהמחברים הנחוצים. (מקור תמונה: Analog Devices)

איור 9: המערכת השלמה למדידת זרם המבוססת על ה-ADAQ23878 μModule היא קטנה יותר מהמחברים הנחוצים. (מקור תמונה: Analog Devices)

מסקנה

מתכננים של ציוד בדיקה ומדידה דורשים דיוק, ביצועים וגמישות, תוך כדי גם שמירה על היכולת להגדיר-תצורה מחדש בקלות של התכן הבסיסי כדי לשרת מספר גדול של מקרי שימוש. כמתואר, רכיבים כמו ה-AD3552R DAC כוללים הרבה פרמטרים ניתנים-לתכנות, המאפשרים להם להיות תפורים כנדרש במהירות ובקלות. ביחד עם ה-ADAQ23878 ADC ונתמך על ידי כלים כדוגמת LTspice ולוחות הערכה ותוכנה, ה-AD35525 משחק תפקיד מפתח בגישה מבוססת-פלטפורמה לבדיקת תכנון מערכת המספק את הגמישות והביצועים הנדרשים, תוך כדי הקטנה למינימום של הזמן הדרוש להגדרת-תצורה מחדש.

מיאון אחריות: דעות, אמונות ונקודות מבט המובעות על ידי מחברים שונים ו/או משתתפי פורום באתר אינטרנט זה לא בהכרח משקפות את הדעות, האמונות ונקודות המבט של חברת DigiKey או את המדיניות הרשמית של חברת DigiKey.