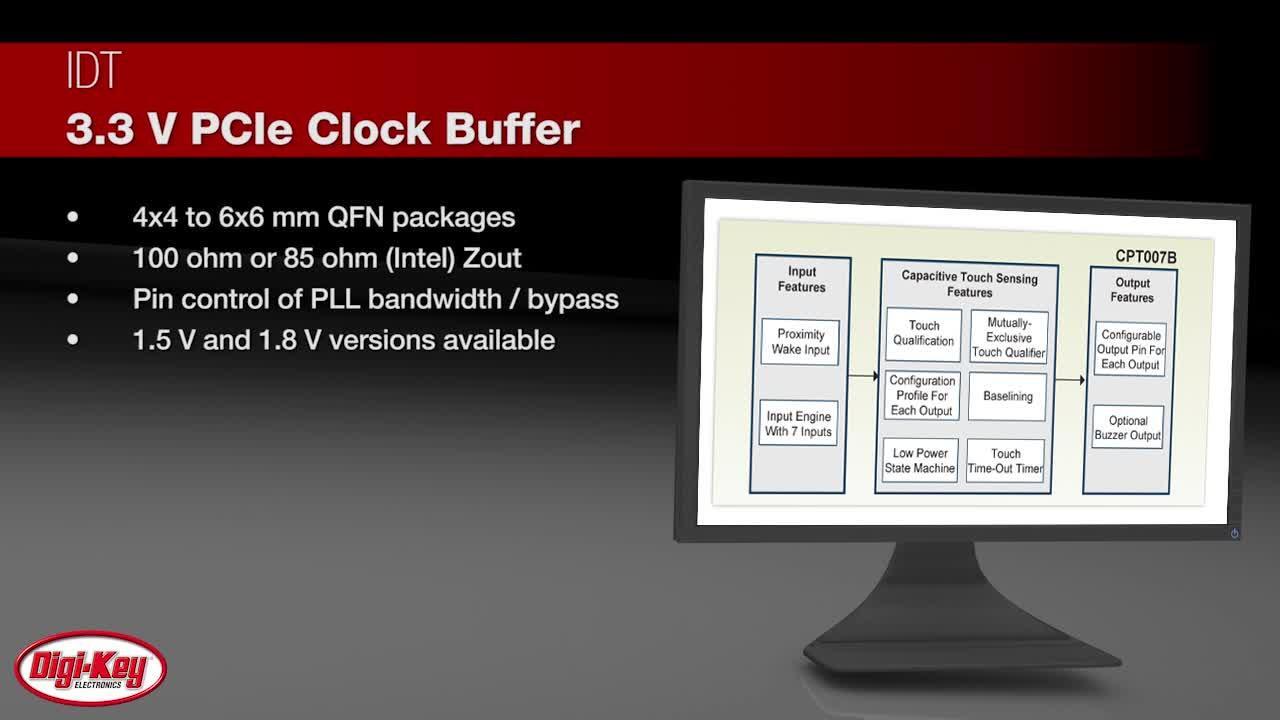

מחולל שעון PCIe 3.3 V

חברת Renesas מציעה תוספת של מחוללי שעון 3.3 V בעלי 6 ו- 8 יציאות לסל מחוללי שעון PCI Express® (PCIe) בהספק נמוך שלה

מחוללי השעון 3.3 V בעלי 6 ו-8 יציאות מבית Renesas פועלים בערך בכחמישית ההספק של התקני שעון PCIe מסורתיים ומבטלים למעשה את השיקולים התרמיים.

מחוללי השעון 3.3 V בעלי 6 ו-8 יציאות מבית Renesas פועלים בערך בכחמישית ההספק של התקני שעון PCIe מסורתיים ומבטלים למעשה את השיקולים התרמיים.

עם הסיומות המשולבות שלהם, המארזים האולטרה-קומפקטיים 5 מ"מ × 5 מ"מ ו-6 מ"מ × 6 מ"מ של ההתקנים 9FGL06 ו-9FGL08 יכולים לספק הפחתה של עד 90 אחוזים משטח הלוח. גרסות ניתנות-לתכנות במפעל מבטיחות אפשרויות מיטוב מהירות כדי לעמוד בדרישות המדויקות של הלקוחות. ההתקנים הידידותיים למערכות-על-שבב (SoC) עולים בהרבה על דרישות ריצוד הפאזה של מפרט ה-PCIe דור 3 מתוך ציפיה ל-PCIe דור 4 המתקרב, והם מתאימים גם עבור יישומים הזקוקים לריצוד פאזה של פחות מ-3 ps rms בתחום התדרים 12 k עד 20 M, כגון Gigabit Ethernet ויישומי ביצועים עיליים אחרים.

התקני ה-3.3 V תואמי-פינים למחוללי שעון PCIe מסדרה 9FGU 1.5 V ומסדרה 9FGV 1.8 V המצליחות ביותר מבית Renesas. משפחת התזמון מתמקדת בתכני הספקת-כוח ובתכנים מוגבלי-שטח הן ביישומים ביתיים והן ביישומי ביצועים עיליים, ומספקת ביצועים ברמת-הארגון תוך הפחתת עלות הבעלות הכוללת. היישומים הפוטנציאליים כוללים מדפסות רב-תכליתיות, שרתים, ממירי טלוויזיה וכונני SSD. המשפחה כולה תואמת PCIe דור 1, 2 ו- 3.

חברת Renesas מתכננת להוסיף במהירות אחרי היצע התחלתי זה את גרסות 3.3 V של חוצצי PCIe בהספק נמוך ומרבבים שהנם תואמי-פינים למשפחות 9DBU/V ו-9DMU/V המצליחות.

משפחת מחוללי שעון PCIe 9FGL כוללת התקנים בעלי 2, 4, 6 או 8 יציאות. מחוללי השעון תומכים הן בארכיטקטורת השעון המשותף PCIe עם/בלי Spread Spectrum, והן בארכיטקטורת שעון הייחוס העצמאי (IR) (ללא-פיזור). ההתקנים מספקים גם עותק של שעון הייחוס, וחוסכים גביש בתכן.

| מאפיינים | ||

|

|

9FGL06

| תמונה | מק"ט יצרן | תיאור | כמות זמינה | מחיר | ||

|---|---|---|---|---|---|---|

|  | 9FGL0641AKILF | IC CLK/FREQ GEN PCIE 40-VFQFN | מיידית - 20 | $13.72 | הצגת הפרטים |