האם ADC יכול להיות רק מחולל מספרים אקראיים?

2025-10-22

כמה טוב הוא ADC? שאלה זו אינה שואלת על מספר הביטים של הרזולוציה; ייתכן שתופתעו לגלות ש-ADC של bit-16 לא תמיד ייתן bit-16 של מידע שימושי! "הרבה ממירי ADC של bit-16 פועלים למעשה כממירי ADC של bit-7 וכמחוללי מספרים אקראיים של bit-9," אומר מייק סטון בספרו "בחירת ממיר ADC". מאמר זה מראה כיצד לקבוע אם ADC מייצר יותר מספרים אקראיים מאשר מספרים שימושיים, יחד עם כמה דרכים פשוטות להפחית את האקראיות.

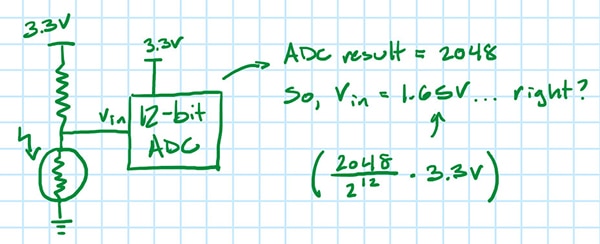

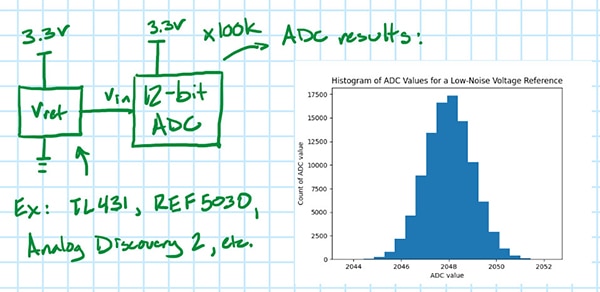

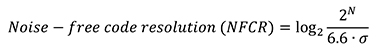

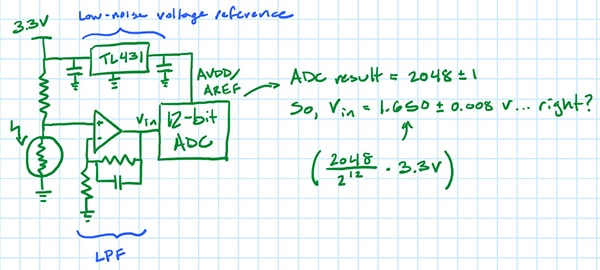

נבחן מערך מפושט: ADC המודד את המתח על פוטו-נגד. אם ה-ADC bit-12 באיור 1 (עם FSV = V 3.3) מדווח על ערך של 2048, האם פירוש הדבר שהמתח על הפוטו-נגד הוא V 1.65?

איור 1: מערך ADC מפושט עבור מדידת מתח על פוטו-נגד. (מקור התמונה: נתן ג'ונס)

איור 1: מערך ADC מפושט עבור מדידת מתח על פוטו-נגד. (מקור התמונה: נתן ג'ונס)

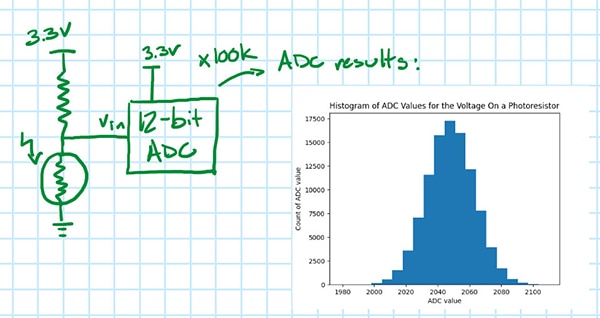

לא, לא ממש! כדי להדגים, קחו דגימה שנייה, אחר כך שלישית, ולמעשה, קחו 100,000 דגימות ורשמו את התוצאות בגרף. מה שיראה הוא התפלגות ערכי ADC (איור 2); אם שום דבר לא השתנה במערך, אזי כל אחד מאלה יכול להיות המתח האמיתי על הפוטו-נגד, כאשר המועמד הסביר ביותר הוא הערך הממוצע של כל הדגימות הללו.

איור 2: מוצגת ההיסטוגרמה של ערכי ADC עבור 100,000 דגימות של מתח הפוטו-נגד. (מקור התמונה: נתן ג'ונס)

איור 2: מוצגת ההיסטוגרמה של ערכי ADC עבור 100,000 דגימות של מתח הפוטו-נגד. (מקור התמונה: נתן ג'ונס)

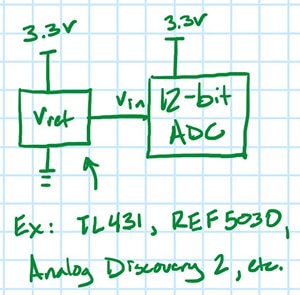

זה מעלה שאלה נוספת. האם חלק מהשוניות האלו יכולות להיות שונויות ממשיות באות הכניסה? כן, זה יכול להיות. כדי לבדוק זאת, המחלק ההתנגדותי יוחלף במתח ייחוס (איור 3) עם רמת רעש ידועה והניסוי יחזור על עצמו.

איור 3: מערך בדיקה חדש עם ייחוס מתח במקום מחלק התנגדות. (מקור התמונה: נתן ג'ונס)

איור 3: מערך בדיקה חדש עם ייחוס מתח במקום מחלק התנגדות. (מקור התמונה: נתן ג'ונס)

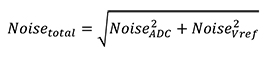

באופן אידיאלי ייחוס המתח בו משתמשים צריך להיות בעל רמת רעש הנמוכה מ-1/3 מרמת הרעש הצפויה ב-ADC (לדוגמה, אם צפוי של-ADC יהיה רעש של LSB 1± [שיהיה mV 0.8± כשמשתמשים ב-ADC בדוגמה לעיל], אז באופן אידיאלי ייחוס המתח צריך להיות בעל רמת רעש הנמוכה מ-ppmV 0.27); אם כך, אזי צפוי שכל הרעש הנמדד חייב להגיע מה-ADC, על בסיס העובדה שרעש ללא-קורלציה מסתכם קוואדראטורית (משוואה 1).

[1]

[1]

אם רעשVref=רעשADC/3 אז הרעשהכולל=1.054 × רעשADC. המשמעות היא שמתח הייחוס תורם רק 5.4% לרעש הכולל, כמות זניחה. אם יתברר שמתח הייחוס רועש יותר מ-1/3 מהרעש מה-ADC, זכרו רק לחסר את תרומתו מסטיית התקן הנמדדת (ראו משוואה 2).

[2]

[2]

כיצד ניתן לדעת את רמת הרעש של מקור מתח

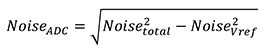

הדרך הקלה ביותר היא למצוא את זה בגיליון הנתונים. הנה דוגמה מגיליון הנתונים של ה-REF5030 של Texas Instruments, המראה שיש לו רמת רעש של ppμV 9.

איור 4: מובאה מגיליון הנתונים של REF5030 המציג את מפרט רעש מתח היציאה. (מקור התמונה: Texas Instruments)

איור 4: מובאה מגיליון הנתונים של REF5030 המציג את מפרט רעש מתח היציאה. (מקור התמונה: Texas Instruments)

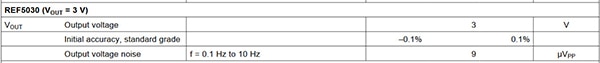

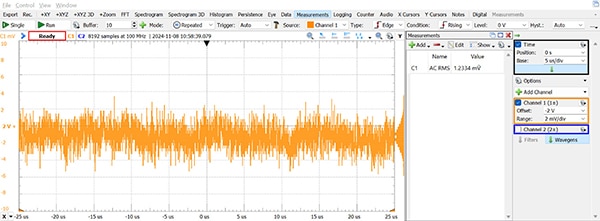

אם גיליון הנתונים אינו מפרט רמת רעש (או רק כדי לאמת את ערכה), פשוט מדדו אותה באמצעות אוסצילוסקופ, אם כי יש לדעת תחילה את רצפת הרעש של האוסצילוסקופ. ניתן לעשות זאת על ידי חיבור אחת מכניסות האוסצילוסקופ להארקה ומדידת ערך ה-RMS של השינויים באות הנצפים. איור 5 מציג את התוצאה של ביצוע פעולה זו עם Analog Discovery 2 (AD2), ומדגים כי רעש RMS הוא כ-mV 0.9. מעניין לציין שערך זה יורד (לתחום ה-µV) אם בסיס הזמן גדל מעבר ל-8 מיקרו-שניות/חלוקה, ככל הנראה משום שה-AD2 משתמש בדגימת-יתר ולאחריה הפחתת-דגימות כדי להגדיל את הרזולוציה האפקטיבית שלו.

איור 5: גרף רמת רצפת הרעש של אוסצילוסקופ Analog Discovery 2. (מקור התמונה: נתן ג'ונס)

איור 5: גרף רמת רצפת הרעש של אוסצילוסקופ Analog Discovery 2. (מקור התמונה: נתן ג'ונס)

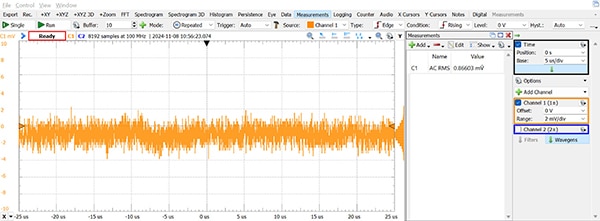

כאשר מודדים את מקור המתח, כל שינוי באות האוסצילוסקופ הוא תוצאה של רעש מצרפי הן במקור המתח והן באוסצילוסקופ. כל עוד מקורות הרעש הללו הם ללא-קורלציה (והם כן), אז measuredNoise=Noise²Scope+Noise²Vref)√ ו-רעשVref=(Noise²Measured-Noise²Scope)√, כמו לעיל. כאשר נמדד אות DCV 2 הנוצר על ידי ה-AD2, הרעש נקבע כ-mV 1.2 (איור 6).

איור 6: גרף זה של אות VDC 2 מצביע על כך שרעש האוסצילוסקופ היה mV 1.2. (מקור התמונה: נתן ג'ונס)

איור 6: גרף זה של אות VDC 2 מצביע על כך שרעש האוסצילוסקופ היה mV 1.2. (מקור התמונה: נתן ג'ונס)

זה מצביע על כך שגם למחולל האותות ב-AD2 יש רמת רעש של כ-mV 0.9. זה נמוך מספיק כדי לבדוק ADC של bit-10 (mV 0.9 הוא קצת פחות מ-1/3 של LSB עבור ADC של bit-10 עם קריאת תחום-מלא של V 3.3); עבור כל ADC ברזולוציה גבוהה יותר, רעש זה יצטרך להילקח בחשבון במדידות.

איור 7: מוצגת ההיסטוגרמה החדשה של ערכי ADC עבור 100,000 דגימות של מתח פוטו-נגד עם ייחוס המתח. (מקור התמונה: נתן ג'ונס)

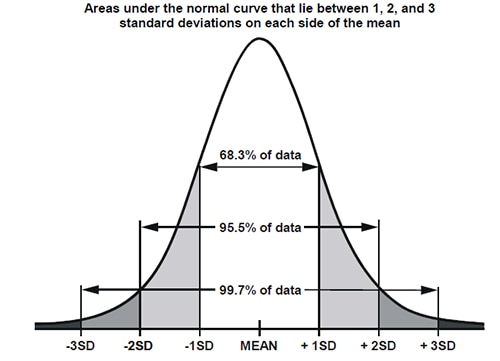

זה הרבה יותר טוב! שימו לב כעת שבהיסטוגרמה השנייה (איור 7) ערכי ציר-x הם רק עד 2052 (להתפלגות בגרף זה [איור 8] יש סטיית תקן של LSB 1), בעוד שערכי הגרף הראשון הם עד 2100 (הייתה לו סטיית תקן של LSB 15). זה נקרא בדיקת היסטוגרמת DC עבור ADC וסטיית התקן מצביעה למעשה על כמות הרעש שיש ב-ADC: בכל פעם שערך נמדד עם ה-ADC, יש סיכוי של 68% בלבד שהערך האמיתי על הפין האנלוגי נמצא למעשה בתחום של ±1 סטיית תקן מאותו ערך, אך יש סיכוי של 99.7% שהערך האמיתי נמצא בתחום של ±3 סטיות תקן מאותו ערך.

איור 8: עקומת התפלגות עם סטיות תקן. (מקור התמונה: https://i.sstatic.net/jkMDV.png)

איור 8: עקומת התפלגות עם סטיות תקן. (מקור התמונה: https://i.sstatic.net/jkMDV.png)

המרת סטיית תקן זו מ-LSBs לוולטים מהווה את הרעש המיוחס-לכניסה עבור ה-ADC (משוואה 3).

![Input - referred noise [V_RMS ]=(σ∙V_FS)/2^N משוואה 3](http://sc-c.digikeyassets.com/-/media/Images/Article%20Library/TechZone%20Articles/2025/October/Can%20an%20ADC%20Be%20Just%20a%20Random%20Number%20Generator/article-2025october-can-an-adc-be-just-equation3.jpg?la=en&ts=6126a5a1-ecae-4e79-bfb0-97e98cce83fa) [3]

[3]

אם ל-ADC יש רעש כה נמוך שכל קודי ה-ADC אכן נופלים לתוך קבוצה (Bin) אחת, נסו להוריד את מתח הייחוס של ה-ADC. רמת הרעש תישאר זהה אך תתפוס יותר קודי ADC מבעבר, מה שיאפשר מציאת ערך נכון עבור הרעש המיוחס-לכניסה.

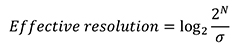

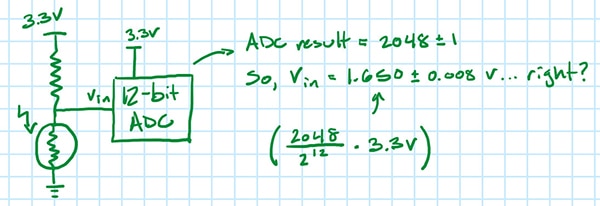

רזולוציה אפקטיבית ורזולוציית קוד נטול-רעש (NFCR) של ה-ADC מייצגות את המידה שבה רעש זה מגביל את רזולוציית ה-ADC, המחושבת על ידי חלוקת התחום המלא של קודי ADC לקבוצות (Bins) שרוחבן הוא סטיית תקן אחת בלבד (משוואה 4) או 6.6 סטיות תקן (משוואה 5).

[4]

[4]

[5]

[5]

בעיקרו של דבר, יש פחות ביטים בפועל בתוצאה מכיוון שיש סיכוי גדול שהביטים האחרונים בתוצאת ה-ADC יהיו שגויים או רועשים.

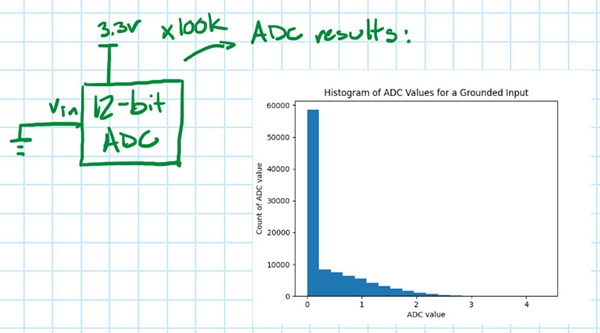

גרסה מעט ישירה יותר של בדיקת היסטוגרמת DC כרוכה פשוט בהארקה של כניסת ה-ADC ולאחר מכן יצירת היסטוגרמה (איור 9) של תוצאות ה-ADC, כפי שנעשה עבור האוסצילוסקופ.

איור 9: מוצגת היסטוגרמה של דגימות מתח היציאה של ה-ADC כאשר הכניסה מחוברת להארקה. (מקור התמונה: נתן ג'ונס)

איור 9: מוצגת היסטוגרמה של דגימות מתח היציאה של ה-ADC כאשר הכניסה מחוברת להארקה. (מקור התמונה: נתן ג'ונס)

סטיית התקן של היסטוגרמה זו היא גם מדד לרעש ה-ADC (מינוס כל תרומה מרעש במתח הייחוס של ה-ADC, שלא ישפיע על קריאות של 0 וולט), אך היא נמוכה באופן אופטימי. ה-ADC כנראה מדווח על ערכים קטנים מ-0 וולט כ-0 בלבד, כך שרק מחצית מהתפלגות הרעש האמיתית נראית. במקרה זה, ניתן לבצע קירוב של רעש ה-ADC אם מניחים שההתפלגות סימטרית סביב ערכה הממוצע, תוך שינוי מספיק מערכי החציון למספרים שליליים כך שההתפלגות תהפוך לסימטרית ולאחר מכן חישוב סטיית התקן שלה (איור 10).

איור 10: שיקוף ההיסטוגרמה של איור 9 כדי עבור קירוב רעש ה-ADC. (מקור התמונה: נתן ג'ונס)

איור 10: שיקוף ההיסטוגרמה של איור 9 כדי עבור קירוב רעש ה-ADC. (מקור התמונה: נתן ג'ונס)

אוקיי, אז מה אפשר לעשות עם כל הרעש הזה? אם הרזולוציה של ה-ADC היא עדיין נמצאת בתחום דרישות הפרויקט (מזל!), קחו בחשבון שכל מדידה של ADC מגיעה עם אי ודאות מסוימת:

- בעת השוואה בין שני ערכי ADC, יש להתייחס אליהם כאל אקוויוולנטיים רק אם הם נמצאים בתחום של 6.6 סטיות תקן (σ) זה מזה (כדי להיות בטוחים ב-99.7% בהשוואה) או אם הם נמצאים בתחום של סטיית תקן אחת זה מזה (כדי להיות בטוחים ב-68% בלבד).

- בעת השוואה בין ערך ADC לבין הסף, הוסיפו היסטרזיס להשוואת הסף (כמו שעושה תרמוסטט) כדי למנוע מהמערכת המשובצת להתניע-מחדש מעל ומתחת לסף זה אך ורק על בסיס רעש.

אם יתברר שה-ADC אינו עומד עוד בדרישות הפרויקט, ישנם כמה דברים פשוטים שניתן לנסות כדי לשפר את ביצועיו. בצד החומרה, אלה כוללים:

- שימוש בייחוס עם רעש נמוך יותר (כגון REF5030 או TL431 EVVO של Texas Instruments) עבור AVCC ו-AREF

- הבטחת ערב-דיבור (Crosstalk) מינימלי בין אותות אנלוגיים ודיגיטליים על ה-PCB

- כיבוי ה-CPU במהלך המרות ADC (אם המיקרו-בקר תומך בכך), כדי להפחית רעש דיגיטלי

בצד התוכנה, ניתן לבצע דגימת-יתר על אות הכניסה (כלומר, לקחת את הממוצע של N דגימות) כדי להפחית רעש, אם כי זה יפחית בבירור את קצב הדגימה המקסימלי. (למעשה, ניתן להשתמש בטכניקה הנקראת "דגימת יתר והפחתת דגימות" כדי להגדיל את הרזולוציה של ה-ADC במידה הקשורה למספר הפעמים שהכניסה עוברת דגימת-יתר!)

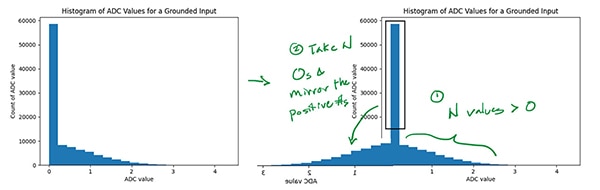

נניח שסטיית התקן של בדיקת היסטוגרמה DC עבור המערך הראשוני היא LSB 1. אם ה-ADC קורא 2048, האם כעת זה אומר (יש סיכוי של 68%) שהערך האמיתי הוא 1.650±0.008? V (איור 11)?

איור 11: בהנחה שסטיית התקן של המערך שבאיור 1 היא LSB 1 ויציאת ה-ADC הא 2048, האם מתח הכניסה האמיתי הוא 1.650±0.008 וולט? (מקור התמונה: נתן ג'ונס)

איור 11: בהנחה שסטיית התקן של המערך שבאיור 1 היא LSB 1 ויציאת ה-ADC הא 2048, האם מתח הכניסה האמיתי הוא 1.650±0.008 וולט? (מקור התמונה: נתן ג'ונס)

קרוב יותר, אך עדיין לא! הסיבה לכך היא שכל ה-ADCs יתקשו במדידת אות כניסה המשתנה במהירות בתדר מסוים, כאשר התוצאה היא מדידות לא מדויקות (לדוגמה, רעש). באופן מפתיע, התדירות שבה זה קורה עשויה להיות נמוכה בהרבה מקצב הדגימה המקסימלי עבור ה-ADC! משמעות הדבר היא שייתכן של-ADC של bit-12 עם קצב דגימה של MSPS 1 (מגה-דגימות לשנייה) אין למעשה רזולוציה של bit-12 עבור אותות כניסה הקרובים ל-kHz 500; הרזולוציה של אותו ADC עשויה לרדת ל-bit-6 או פחות כאשר תדר אות הכניסה הוא כה גבוה. אם מנסים למדוד אות על הפוטו-נגד שהוא מעל Hz 10, ייתכן של-ADC אין למעשה רזולוציה של bit-12.

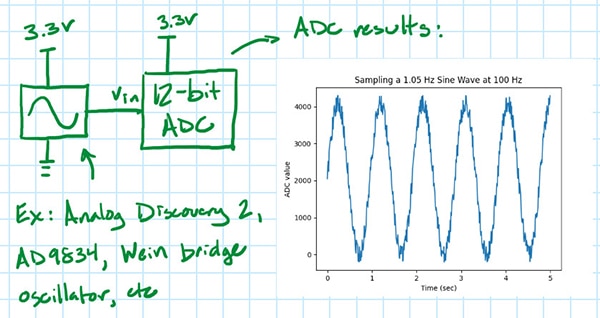

כדי לקבוע עד כמה הרזולוציה של ה-ADC עומדת בתדרי כניסה גבוהים יותר, יש לשלוח אות הידוע כתקין (הפעם, גל סינוס) ולמדוד עד כמה ערכי ה-ADC תואמים לאות הידוע כתקין (איור 12). האם גל הסינוס "הוא מספיק טוב"? נדון בזה לאחר שנגלה הליך ביצוע הבדיקה; זה יהיה הגיוני יותר כך.)

איור 12: מערך בדיקה עם כניסה גל סינוס הידוע כתקין. (מקור התמונה: נתן ג'ונס)

איור 12: מערך בדיקה עם כניסה גל סינוס הידוע כתקין. (מקור התמונה: נתן ג'ונס)

עבור גל הסינוס, ניתן להשתמש במחולל פונקציות (כמו אלה הנמצאים באוסצילוסקופים רבים עם חיבור USB), שבב DDS (כמו ה-AD9834 של Analog Devices), או להרכיב מחולל גל סינוס מותאם-במיוחד (לדוגמה, המבוסס על מתנד גשר Wien או באמצעות ה-MAX7400 של Analog Devices מסנן מעביר-נמוכים של גל ריבועי). חשוב לציין כי עבור בדיקה זו יש להשתמש אך ורק בתדרי כניסה אשר אינם כפולות שלמות של תדר הדגימה (למשל, אין להשתמש בתדר כניסה של kHz 1 אם קצב הדגימה הוא kHz 100). זאת כדי למנוע דגימה שגויה של גל הסינוס באותם מיקומים בכל מחזור. בנוסף, כדי להפעיל את ה-ADC בצורה מקסימלית, יש להשתמש באמפליטודת גל סינוס כניסה בערך הגדול ביותר שאינו "מהדק" את היציאה (למשל, משהו מעט קטן מ-V 1.65 עבור ה-ADC בדוגמאות לעיל).

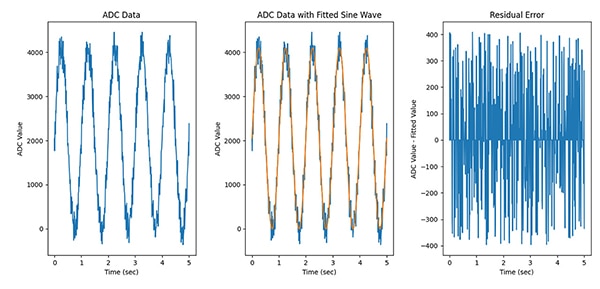

לאחר איסוף תוצאות ה-ADC, הנתונים מותאמים לגל סינוס כדי לחשב את השגיאה השיורית. ניתן לבצע את התאמת גל הסינוס עם כמעט כל כמות נתונים, אך כדי לקבל את התוצאות הטובות ביותר, צריכים להיות לפחות חמישה מחזורים מלאים של גל סינוס בכניסה. סביר להניח שיהיה צורך לאתחל את אלגוריתם התאמת הסינוס על ידי מתן ניחושים ראשוניים עבור האמפליטודה, התדר, היסט הפאזה והאופסט (איור 13).

איור 13: באמצעות אלגוריתם התאמת גל סינוס, ניתן לקבוע את השגיאה השיורית. (מקור התמונה: נתן ג'ונס)

איור 13: באמצעות אלגוריתם התאמת גל סינוס, ניתן לקבוע את השגיאה השיורית. (מקור התמונה: נתן ג'ונס)

בדיקה זו נקראת מבחן התאמת גל סינוס עבור ADC, וערך RMS של השגיאה השיורית הוא מדד לכמה רועש ה-ADC בתדר כניסה ספציפי זה. בתדרים נמוכים יותר, רעש RMS אמור להתאים לרעש המיוחס לכניסה מבדיקת היסטוגרמת ה-DC, אך בתדרים גבוהים יותר הוא כמעט בוודאות יפחת כתוצאה ממקורות רעש תלויי-תדר שהוזכרו לעיל.

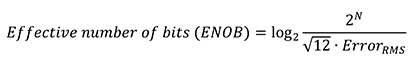

ניתן להשתמש בערך הרעש RMS ממבחן ההתאמה של גל הסינוס כדי לחשב את מספר הביטים האפקטיבי (ENOB) של ה-ADC (משוואה 6), שהוא מספר הביטים של ADC אידיאלי שמקור הרעש היחיד שלו, רעש קוונטיזציה, הוא בעל ערך RMS זהה לרעש ב-ADC.

[6]

[6]

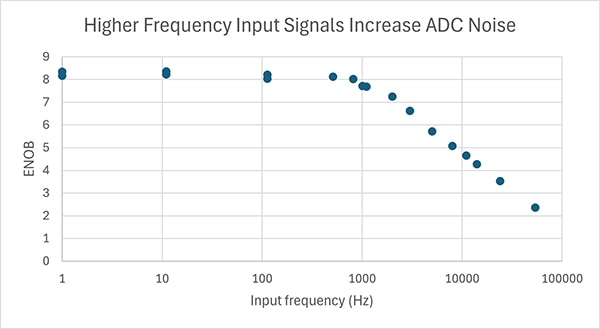

ערך זה הוא ספציפי לתדר אות הכניסה בו משתמשים. כדי לקבל תמונה מלאה יותר של ה-ADC, יש לחזור על בדיקה זו בתדרים עד לאות הכניסה הגבוה ביותר הרלוונטי, או עד מחצית מקצב הדגימה המקסימלי. ייתכן שיתגלה שהרעש עולה משמעותית (וה-ENOB יורד משמעותית!) בתדרים הנמוכים בהרבה ממחצית מקצב הדגימה המקסימלי! לדוגמה, סדרת בדיקות מדויקת זו בוצעה על ה-ADC ב-STM32F042K6 של STMicroelectronics והתוצאות הוצגו בגרף (איור 14).

איור 14: בדיקת רעש תדר עבור ADC במיקרו-בקר STM32F042K6. (מקור התמונה: נתן ג'ונס)

איור 14: בדיקת רעש תדר עבור ADC במיקרו-בקר STM32F042K6. (מקור התמונה: נתן ג'ונס)

למרות שה-ADC במיקרו-בקר STM32F042K6 יכול לדגום בתדר של 1 מגה-הרץ, הרזולוציה יורדת מעל 1 קילו-הרץ; אם הכוונה הייתה למדוד אות של 10 קילו-הרץ עם ADC זה, היו רק כ-5 ביטים של רזולוציה בנקודה זו! (שימו לב גם ש-ENOB המקסימלי הוא בסביבות 8.3; זה נובע מרעש של כ-LSBs 10 אפילו ב-DC, מה שמפחית את הרזולוציה האפקטיבית של ה-ADC מ-bit-12 לכ-bit 8.7 כבר מההתחלה). בדיקות אלו נערכו על לוח פיתוח Nucleo-F042 שלא עבר שינוי; התוצאות יהיו טובות בהרבה אם נעשה שימוש באחת מהטכניקות שהוזכרו לעיל ["אוקיי, אז מה אפשר לעשות עם כל הרעש הזה?"].)

כיצד ניתן לדעת את רמת הרעש של גל סינוס

כמו עם ייחוס המתח, אם רמת הרעש של גל סינוס היא אפריורי (כלומר, אם היא אינה זמינה בגיליון הנתונים), אזי יש צורך למדוד אותה באמצעות אוסצילוסקופ. השימוש בטכניקת התאמת גל סינוס שנדונה קודם לכן יכול לאפיין את הרעש ממחולל גל סינוס.

- ראשית, קבעו את רמת הרעש של האוסצילוסקופ על ידי חיבור הכניסה שלו להארקה וחישוב ערך RMS של היציאה (כמתואר קודם לכן בסעיף "כיצד ניתן לדעת מה רמת הרעש של מקור מתח").

- לאחר מכן, מדדו את היציאה ממחולל גל סינוס, התאימו את התוצאות לגל סינוס מושלם וחשבו את ערך RMS של השיוריות. לאחר מכן השתמשו במשוואה 2 כדי לקבוע את הרעש של מחולל גל סינוס (תוך שימוש ברצפת הרעש של האוסצילוסקופ כקירוב לרעש AC שלו).

- יש להבטיח שאימפדנס היציאה של ההתקן המחובר לפין האנלוגי היא נמוכה מאוד, אולי הוספת מגבר שרת עבור חציצה (Buffering)

- כוונון שעון ה-ADC או זמן הדגימה/החזקה שלו כך שיהיו מהירים ככל האפשר, תוך מתן מספיק זמן לקבל הפנימי להיטען

- שימוש במקור שעון ADC עם ריצוד נמוך וקביעת תצורת המערכת ללקיחת דגימות ADC במרווחי זמן קבועים

- אפיון ADC של Raspberry Pi Pico

- הבנת ממירי נתונים (Texas Instruments)

- הבנת SINAD, ENOB, SNR, THD, THD + N ו-SFDR כדי שלא תלכו לאיבוד ברצפת הרעש (Analog Devices)

- היבטי הטוב, הרע והמכוער של רעש כניסת ADC - האם היעדר רעש הוא טוב? (Analog Devices(

- הפקת את המקסימום מה-ADC של SAM D21 (Thea Codes)

- "בדיקת ממיר אנלוגי-לדיגיטלי" (קנט לונדברג)

- בדיקות דינמיות עבור ביצועי ממיר A/D (Texas Instruments)

- כיצד למטב את דיוק ה-ADC במיקרו-בקרים STM32 (STM)

- שיפור רזולוציית ADC על ידי דגימת-יתר (Atmel)

- יסודות ניתוח רעשי ADC מדויק (Texas Instruments)

- כיול שגיאות הגבר ואופסט של ADC על מיקרו-בקרים מבוססי +ARM® Cortex®-M0 (Microchip)

- יצירת גל סינוס באמצעות סינון מעביר-נמוכים של גל ריבועי

- הבנת ההשפעה של רעש הדיגיטציה על מדידות אוסצילוסקופ (EE Times)

- הבנת מספר הביטים האפקטיבי (Robust Circuit Design)

באופן אידיאלי, רמת הרעש של גל סינוס נמוכה מ-1/3 מרמת הרעש הצפויה מה-ADC (במילים אחרות, גל הסינוס הוא "טהור מבחינה ספקטרלית"), מה שהופך את תרומתו לרעש הנמדד לזניחה. אם רמת הרעש של גל הסינוס גבוהה מכך, זכרו להפחית אותה מהרעש הנמדד המתקבל מחישוב ערכי RMS של השגיאה השיורית.

יש לחזור על בדיקה זו עבור כל תדר כניסה המיועד לשמש לבדיקת ה-ADC (אפילו למחולל גל סינוס עשויים להיות מקורות רעש תלויי-תדר!).

מה אפשר לעשות עם כל הרעש הזה? ראשית, מומלץ להתקין מסנן מעביר-נמוכים (LPF) בין מקור האות ל-ADC, עם תדר קיטעון ממש מעל האות הגבוה ביותר הרצוי, כדי לסייע בהגבלת רעש בתדר גבוה (זה "דבר טוב לעשות", באופן כללי, עבור כל מערכת קליטת נתונים). אם אות התדר הגבוה ביותר שמעניין אתכם נמצא מתחת ל"ברך" בגרף של ENOB לעומת תדר הכניסה, אזי אין באמת הפסדי רזולוציה. כאשר מנסים למדוד אותות מעל "הברך" הזו, ישנם כמה דברים שכדאי לנסות כדי לשפר את הרזולוציה בתדרים גבוהים יותר. אלה כוללים:

אלא אם כן המטרה היא אות בפס תדרים צר מאוד, הדבר הפשוט ביותר לעשות לאחר מכן הוא להניח כי לאותות הכניסה בפועל יש תוכן תדרים שווה מ-DC ועד תדר הקיטעון של ה-LPF, ולכן רעש RMS בכל מדידת ADC הוא רעש RMS ממוצע הנמדד באמצעות מבחן התאמת גל סינוס מ-DC ועד תדר הקיטעון. אם רוצים למדוד אותות פס-רחב עד 10 קילו-הרץ באמצעות ה-STM32F042K6 שנדון קודם לכן, עדיף לפעול כאילו ל-ADC יש רק ENOB של כ-6 ביטים עבור כל מדידה. ערך זה עשוי בהחלט להיות נמוך מאוד מזה שנקבע באמצעות מבחן היסטוגרמת DC, דבר המצביע על כך שיש פחות ודאות בכל אחת ממדידות ה-ADC אם קיימת אפשרות שיש להן תוכן תדר גבוה יותר.

ההנחה הבאה שיש לקחת בחשבון היא הוספת LPF בין החיישן ל-ADC כך שרעש RMS מ-DC עד לתדר הקיטעון יהיה רק LSB 1±. אם ה-ADC קורא 2048, האם כעת זה אומר (יש סיכוי של 68%) שהערך האמיתי הוא 1.650±0.008 וולט (איור 15)?

איור 15: האם הוספת מסנן מעביר-נמוכים במעגל מביאה לערך אמיתי של 1.650±0.008 וולט? (מקור התמונה: נתן ג'ונס)

איור 15: האם הוספת מסנן מעביר-נמוכים במעגל מביאה לערך אמיתי של 1.650±0.008 וולט? (מקור התמונה: נתן ג'ונס)

כמה שזה נשמע מטורף, עדיין לא! למרות שמאמר זה אפיין למעשה את הרעש ב-ADC, הוא עדיין לא אפיין את השגיאה שלו. לאחר הבדיקה המתוארת כאן, הוודאות היחידה היא ששני ערכי ADC הם אותם או שונים. עם זאת, לא ידוע האם קוד ADC של 2048 מתאים בדיוק ל-1.65 וולט או למשהו אחר. שגיאות אי-לינאריות של הגבר, אופסט ודיפרנציאליות (בין היתר) משמעותן עלולה להיות שהמרה מקוד ADC למתח ממשי היא מסובכת יותר משימוש ב-Vin=ADC result × VFS/2N. אך זה נושא למאמר אחר!

מקורות

מיאון אחריות: דעות, אמונות ונקודות מבט המובעות על ידי מחברים שונים ו/או משתתפי פורום באתר אינטרנט זה לא בהכרח משקפות את הדעות, האמונות ונקודות המבט של חברת DigiKey או את המדיניות הרשמית של חברת DigiKey.