כיצד להשתמש במערכות FPGA SoC עבור מערכות זמן-אמת קשיחות, מחוברות ומאובטחות

באדיבות ‎DigiKey's North American Editors

2023-02-16

מערכי שערים ניתנים-לתכנות בשטח (FPGAs), תת-מערכות יחידת מיקרו-בקר (MCU) RISC-V בעלת יכולת Linux, ארכיטקטורות זיכרון מתקדמות וממשקי תקשורת ביצועים-עיליים הם כלים חשובים עבור מתכננים. זה נכון במיוחד עבור מתכננים של מערכות מחוברות מאובטחות, מערכות קריטיות-לבטיחות, ומגוון רחב של מערכות זמן-אמת קשיחות דטרמינסטיות כמו בינה מלאכותית (AI) ולמידת מכונה (ML).

עם זאת, השילוב של אלמנטים מגוונים אלה למערכת מאובטחת, מחוברת ודטרמינסטית יכול להיות עיסוק מאתגר וגוזל-זמן, כפי שהיא גם הפריסה של חברורי מהירות-גבוהה עבור האלמנטים השונים של המערכת. מתכננים נדרשים לכלול יחידת ניהול זיכרון, יחידת הגנה על זיכרון, יכולת אתחול (Boot) מאובטח ומקמ"שים בקטגוריה Gigabit עבור חיבוריות מהירות-גבוהה. התכנון ידרוש ניהול הספק אקטיבי וסטטי ובקרה של זרמי התנעה (inrush currents). תכנים מסוימים יידרשו לעבוד בתחום הטמפרטורות המסחרי המורחב של טמפרטורת צומת (TJ) °0 עד 100°C+, בעוד מערכות בסביבות תעשייתיות תידרשנה לעבוד עם TJ מ-C°40- עד C°100+.

כדי לענות על אתגרים אלה ואחרים, מתכננים יכולים לפנות אל התקני מערכת-על-שבב (SoC) FPGA המשלבים צריכת הספק נמוכה, נצילות תרמית ואבטחה בדרגת הגנה עבור מערכות חכמות, מחוברות ודטרמיניסטיות.

מאמר זה סוקר את הארכיטקטורה של מערכת FPGA SoC כזאת וכיצד היא תומכת בתכנון היעיל של מערכות מחוברות ודטרמיניסטיות. אחר כך המאמר מציג בקצרה את כוח העיבוד של ה-EEMBC CoreMark-Pro לעומת אמת מידה של צריכת הספק, יחד עם מבט על ביצועי אמת מידה של מערכת FPGA SoC מיצגת. הוא מסתכל על כיצד אפויה אבטחה בתוך מערכות FPGA SoC אלו ונותן פירוט על מערכות דוגמה של FPGA SoC מבית Microchip Technology, יחד עם פלטפורמת פיתוח כדי להאיץ את תהליך התכנון. המאמר מסיים עם רשימה קצרה של לוחות הרחבה מבית MikroElektronika הניתנים לשימוש במגוון ממשקי תקשורת, כמו גם יכולת איתור Global Navigation Satellite System (GNSS).

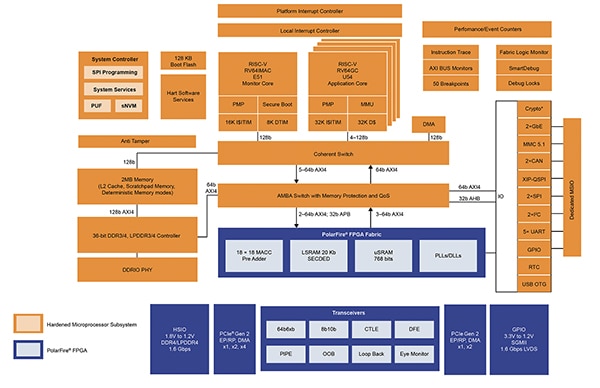

מערכות SoC בנויות עם מארג FPGA

ה‘שבב’ עבור SoC זה הוא מארג FPGA המכיל את האלמנטים של המערכת, מה-FPGA עד לתת-מערכת RISC-V MCU הבנויה עם לוגיקת FPGA מוקשחת. תת-המערכת MCU כוללת מקבץ RISC-V MCU ארבע-ליבות, בקר מערכת ותת-מערכת זיכרון רמה 2 (L2) דטרמיניסטית. ה-FPGA במערכות SoC אלו כולל עד 460 K אלמנטים לוגיים, מקמ"שים של עד 12.7 גיגה-ביט לשנייה (Gbps) ובלוקים אחרים של כניסה/יציאה (I/O) כולל I/O למטרה כללית (GPIO) ו-Peripheral Component Interconnect Express (PCIe) 2. הארכיטקטורה הכוללת מתוכננת לאמינות. היא כוללת תיקון-שגיאה-יחידה וגילוי-שגיאה-כפולה (SECDED) בכל הזיכרונות, ניתוח הספק דיפרנציאלי (differential power analysis) (DPA), הגנת זיכרון פיזי (physical memory protection) ו-128 קילו-ביט (Kbits) של זיכרון אתחול Flash (איור 1).

איור 1: כל האלמנטים במערכת FPGA SoC זו, כולל תת-המערכות RISC-V, ממומשים על מארג ה-FPGA. (מקור תמונה: Microchip Technology)

איור 1: כל האלמנטים במערכת FPGA SoC זו, כולל תת-המערכות RISC-V, ממומשים על מארג ה-FPGA. (מקור תמונה: Microchip Technology)

חברת Microchip מציעה את המערכת האקולוגית שלה Mi-V (מבוטאת “my five”) של כלים ומשאבי תכנון צד-שלישי לתמיכה במימוש של מערכות RISC-V. היא בנויה להאיץ את אימוץ ארכיטקטורת סט הפקודות (ISA) של ה-RISC-V עבור ליבות RISC-V מוקשחות ועבור ליבות RISC-V רכות. האלמנטים של המערכת האקולוגית Mi-V כוללים גישה אל:

- רישיונות קניין רוחני (IP)

- חומרה

- מערכות הפעלה ותוכנת ביניים (middleware)

- מנפי-באגים, קומפיילרים ושירותי תכנון

יחידות ה-RISC-V MCU המוקשחות ב-FPGA SoC כוללות מספר יכולות ניפוי-באגים כמו passive run-time configurable advanced extensible interface (AXI) ו-instruction trace. ה-AXI מאפשר למתכננים לנטר נתונים הנכתבים או נקראים בזיכרונות שונים ולדעת מתי נכתבים או נקראים.

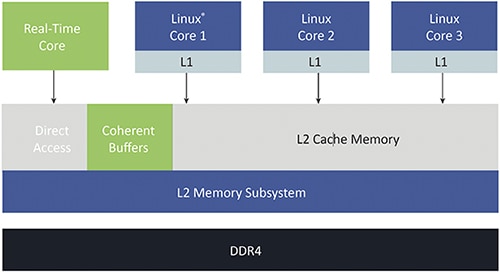

תת-המערכת RISC-V MCU משתמשת בצינור מידע בסדר מסוים, שטף אחד של חמש דרגות. היא לא פגיעה לנקודות תורפה Spectre או Meltdown היכולות להעמיד במבחן ארכיטקטורות פגומות. כל חמשת יחידות המיקרו-בקר הן קוהרנטיות עם תת-מערכת הזיכרון, תומכות בתמהיל של מערכות זמן-אמת מרובות-עיבוד אסימטריות (AMP) דטרמינסטיות ו-Linux. היכולות של תת-המערכות RISC-V כוללות (איור 2):

- להריץ Linux ופעולות זמן-אמת קשיחות

- להגדיר תצורה של L1 ו-L2 כזיכרון דטרמינסטי

- תת-מערכת זיכרון DDR4

- אפשור/נטרול חוזי הסתעפות (branch predictors)

- פעולת צינור מידע בסדר מסוים

איור 2: תת-המערכת RISC-V כוללת מספר אלמנטים של מעבד וזיכרון. (מקור תמונה: Microchip Technology)

איור 2: תת-המערכת RISC-V כוללת מספר אלמנטים של מעבד וזיכרון. (מקור תמונה: Microchip Technology)

יותר עיבוד בפחות אנרגיה

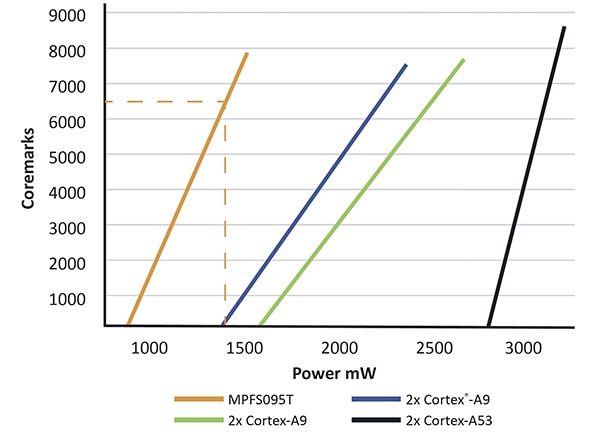

נוסף ליתרונות פעולת המערכת שלהן, כולל תמיכה בעיבוד זמן-אמת קשיח, מערכות FPGA SoC אלו הן יעילות ביותר אנרגטית. אמת המידה EEMBC CoreMark-PRO היא תקן תעשייה עבור השוואת הנצילות והביצועים של יחידות מיקרו-בקר במערכות משובצות. היא תוכננה במיוחד עבור הערכת והשוואת ביצועי חומרה ולהחליף את אמת המידה Dhrystone.

עומסי העבודה CoreMark-PRO כוללים מגוון של מאפייני ביצועים, הקבלות ברמת-הוראות וניצול זיכרון מבוסס על ארבעה עומסי עבודה של נקודה-צפה וחמישה עומסי עבודה נפוצים של מספרים שלמים. עומסי העבודה של נקודה-צפה כוללים רוטינה של אלגברה לינארית הנגזרת מ-LINPACK, התמרת Fourier מהירה, אלגוריתם רשת עצבית עבור הערכת תבנית, וגרסה משופרת של אמת המידה Livermore loops. דחיסת JPEG, XML parser, דחיסת ZIP, ופונקציות 256-bit secure hash algorithm (SHA-256) יוצרות את הבסיס של עומסי העבודה מספר שלם (integer workloads).

דגמי ה-MPFSO95T של רכיבי SoC FPGA אלו, כמו ה-MPFS095TL-FCSG536E, יכולים לספק עד 6,500 Coremarks ב-1.3 ואט (איור 3).

איור 3: ה-MPFS095T FPGA SoC (קו כתום) מספק 6500 Coremarks ב-1.3 ואט. (מקור תמונה: Microchip Technology)

איור 3: ה-MPFS095T FPGA SoC (קו כתום) מספק 6500 Coremarks ב-1.3 ואט. (מקור תמונה: Microchip Technology)

שיקולי אבטחה

יישומי זמן-אמת קשיחים וקריטיים-לבטיחות עבור מערכות FPGA SoC אלו דורשים אבטחה חזקה בנוסף לנצילות אנרגיה גבוהה ויכולות עיבוד רבות-עוצמה. פונקציות האבטחה הבסיסיות של מערכות FPGA SoC אלו כוללות תכנות Bitstream חסין ניתוח הספק דיפרנציאלי (differential power analysis) (DPA), מחולל מספר אקראי אמיתי (TRNG) ו-Physically Unclonable Function (PUF). הם גם כוללים אתחול (Boot) מאובטח סטנדרטי ומוגדר-משתמש, הגנה על זיכרון פיזי המספקת מגבלות גישה לזיכרון בהתיחס למצב ההרשאה של המכונה, כולל אופני פעולת מכונה, מפקח או משתמש, וחסינות מפני התקפות Meltdown ו-Spectre.

אבטחה מתחילה עם ניהול שרשרת אספקה מאובטחת, כולל השימוש במודולי אבטחת חומרה (HSMs) במהלך בדיקת ואריזת פרוסת סיליקון. השימוש באישור x.509 FPGA חתום דיגיטלית ב-768-byte ומשובץ בכל מערכת FPGA SoC מוסיף לביטחון שרשרת האספקה.

במערכות FPGA SoC אלו כלולים מספר גלאי נסיון-חבלה על-השבב, כדי להבטיח עבודה מאובטחת ואמינה. אם מגלים נסיון-חבלה, מורם דגלון חבלה המאפשר למערכת להגיב לפי הצורך. חלק מגלאי נסיון-החבלה הקיימים כוללים:

- מנטרי מתח

- חיישני טמפרטורה

- גלאי תקלת שעון (Clock glitch) ותדר שעון

- גלאי אקטיבי JTAG

- גלאי אקטיבי Mesh

האבטחה מובטחת עוד יותר עם אמצעי-נגד 256-bit advanced encryption standard (AES-256) symmetric block cipher correlation power attack (CPA), יכולות cryptographic digest משולבות כדי להבטיח אמינות נתונים (data integrity), PUF משולב עבור אחסון מפתח ויכולות מחיקה של פרמטרים רגישים (zeroization) במארג ה-FPGA וכל הזיכרונות על-השבב.

דוגמאות FPGA SoC

Microchip Technology משלבת יכולות וטכנולוגיות אלו במערכות PolarFire FPGA SoC עם דרגות מהירות מרובות, דרוגי טמפרטורה וגדלי מארז שונים, כדי לתמוך בצרכי מתכננים לתחום רחב של פתרונות עם בין 25 K ו-460 K אלמנטים לוגיים. קיימות ארבע דרגות טמפרטורה (כולן מדורגות עבור TJ), תחום מסחרי מורחב 0°C עד 100°C+, תחום תעשייתי 40°C- עד 100°C+, תחום רכב 40°C- עד 125°C+ ותחום צבאי 55°C- עד 125°C+.

מתכננים יכולים לבחור מהתקנים בדרגת מהירות סטנדרטית, או התקנים בדרגת מהירות 1- שהם מהירים יותר ב-15%. מערכות FPGA SoC אלו ניתנות להפעלה ב-1.0 וולט עבור עבודה בהספק הנמוך ביותר, או ב-1.05 וולט עבור ביצועים גבוהים יותר. הן זמינות במגוון גדלי מארז, כולל 11 X 11 מילימטר (mm), 16 X 16 מ"מ, ו-19 x 19 מ"מ.

עבור יישומים הדורשים עבודה בטמפרטורה מסחרית מורחבת, עבודה במהירות סטנדרטית ו-254 K אלמנטים לוגיים במארז של 19 X 19 מ"מ, מתכננים יכולים להשתמש ב-MPFS250T-FCVG484EES. עבור פתרונות פשוטים יותר הדורשים 23 K אלמנטים לוגיים, מתכננים יכולים לפנות אל ה-MPFS025T-FCVG484E, גם כן עם עבודה בטמפרטורה מסחרית מורחבת, דרגת מהירות סטנדרטית ומארז של 19 x 19 מ"מ. ה-MPFS250T-1FCSG536T2 עם 254 K אלמנטים לוגיים מתוכננת עבור מערכות רכב ביצועים-עיליים והיא בעלת תחום טמפרטורות עבודה של 40- עד Cִ°125 ודרגת מהירות 1- עבור שעון מהיר יותר ב-15%, במארז קומפקטי 16 X 16 מ"מ עם 536 כדוריות בפסיעה של 0.5 מ"מ (איור 4).

איור 4: ה-MPFS250T-1FCSG536T2 לטמפרטורת רכב מגיעה במארז 16 X 16 מ"מ עם 536 כדוריות ופסיעה של 0.5 מ"מ. (מקור תמונה: Microchip Technology)

איור 4: ה-MPFS250T-1FCSG536T2 לטמפרטורת רכב מגיעה במארז 16 X 16 מ"מ עם 536 כדוריות ופסיעה של 0.5 מ"מ. (מקור תמונה: Microchip Technology)

פלטפורמת פיתוח FPGA SoC

כדי לזרז את התכנון של מערכות עם ה-PolarFire FPGA SoC, חברת Microchip מציעה את ערכת ה-MPFS-ICICLE-KIT-ES PolarFire SoC Icicle המאפשרת חקר של תת-מערכת המיקרו-מעבד RISC-V חמש-ליבות בעל יכולת-Linux עם ביצועי זמן-אמת בהספק-נמוך. הערכה כוללת רישיון חינמי Libero Silver הדרוש להערכת תכנים. הערכה תומכת במאפייני תכנות וניפוי-באגים בשפה יחידה.

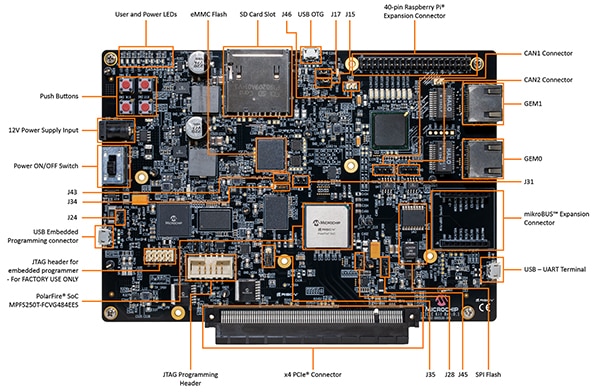

מערכות FPGA SoC אלו נתמכות על ידי ערכת פיתוח התוכנה (SDK) מאיץ VectorBlox המאפשרת יישומי AI/ML בעלי גורם-צורה-קטן, הספק נמוך. הדגש הוא על פישוט תהליך התכנון עד לנקודה שמתכננים אינם נדרשים להיות בעלי ניסיון בתכנון FPGA. ה-VectorBlox Accelerator SDK מאפשרת למפתחים לתכנת רשתות נוירוניות נצילות-הספק תוך שימוש ב-++C/C. לערכת ה-Icicle יש מספר מאפיינים כדי לספק סביבת פיתוח מקיפה, כולל מערכת חיישן אספקת-כוח מרובת-פסי-מתח כדי לנטר את אשכולות אספקת-הכוח השונים, נקודת יציאה מקור PCIe (PCIe root port), וזיכרונות על-הלוח—כולל LPDDR4, QSPI ו-eMMC Flash—להריץ Linux ו-Raspberry Pi, ונקודות יציאה mikroBUS הרחבה עבור אפשרויות חיבוריות אלחוטית וחוטית רבות, ועוד הרחבות פונקציונליות כמו יכולת איתור GNSS (איור 5).

איור 5: סביבת פיתוח FPGA SoC מקיפה זו כוללת מחברים עבור Raspberry Pi (למעלה ימין) ולוחות הרחבה mikroBUS (למטה ימין). (מקור תמונה: Microchip Technology)

איור 5: סביבת פיתוח FPGA SoC מקיפה זו כוללת מחברים עבור Raspberry Pi (למעלה ימין) ולוחות הרחבה mikroBUS (למטה ימין). (מקור תמונה: Microchip Technology)

לוחות הרחבה

מספר דוגמאות של לוחות הרחבה mikroBUS כוללות:

MIKROE-986, עבור הוספת חיבוריות אפיק CAN תוך שימוש בממשק היקפי טורי (SPI).

MIKROE-1582, עבור ממשק בין ה-MCU ואפיק RS-232.

MIKROE-989, עבור התחברות עם אפיק תקשורת RS422/485.

MIKROE-3144, תומך בטכנולוגיות ה-LTE Cat M1 ו-NB1 המאפשרות חיבוריות אמינה ופשוטה עם התקני 3GPP IoT.

MIKROE-2670, מאפשר פונקציונליות GNSS עם קליטה בו-זמנית של מערכי GPS ו-Galileo ועוד BeiDou או GLONASS, וכתוצאה מכך דיוק מיקום גבוה במצבים עם אותות חלשים או הפרעות בקניונים אורבניים.

מסקנה

כשמפתחים מערכות דטרמינסטיות זמן-אמת קשיחות, קריטיות-לבטיחות, מחוברות, מתכננים יכולים לפנות אל מערכות FPGA SoC. מערכות FPGA SoC מספקות מגוון רחב של אלמנטים של מערכת, כולל מארג FPGA, תת-מערכת RISC-V MCU עם זיכרונות ביצועים-עיליים, ממשקי תקשורת מהירות-גבוהה ופונקציות אבטחה מרובות. כדי לסייע למתכננים בצעדים הראשונים, קיימים לוחות וסביבות פיתוח הכוללים את כל האלמנטים הנחוצים, כולל לוחות הרחבה הניתנים לשימוש עבור מימוש מגוון רחב של תקשורות ופונקציות מיקום.

קריאה מומלצת

מיאון אחריות: דעות, אמונות ונקודות מבט המובעות על ידי מחברים שונים ו/או משתתפי פורום באתר אינטרנט זה לא בהכרח משקפות את הדעות, האמונות ונקודות המבט של חברת DigiKey או את המדיניות הרשמית של חברת DigiKey.