העמידה בדרישות פונקציונליות ובטיחותיות מגוונות עם מעבדים רבי-ליבות

באדיבות ‎DigiKey's North American Editors

2020-10-01

יישומי כלי-רכב, תעשייה, רובוטיקה, בקרת מבנים ומערכו משובצות קריטיות אחרות צפויים להתמודד עם עומסי עבודה מגוונים יותר המתפרשים מניטור בזמן-אמת בהספק-נמוך ועד ליישומי מולטימדיה ברמה גבוהה עם צגי גרפיקה רבי-מסכים עבור ממשקי אדם-מכונה (HMI) . תוך עמידה בדרישות פונקציונליות רחבות אלו, עליהם להיות מסוגלים לתמוך בתקני בטיחות מחמירים, עלות נמוכה יותר, חתימת-שטח קטנה יותר ומיטוב איזון ההספק/ביצועים.

כדי לעמוד בדרישות לעיתים סותרות אלו, נאלצו המפתחים עד עכשיו להקריב יכולת פונקציונלית או לסבך את התכן והייצור עם התקנים נוספים הדרושים לתמיכה בדרישות ספציפיות עבור גרפיקה, אבטחה ובטיחות, בין היתר. מה שמפתחים באמת זקוקים לו הוא פיתרון יחיד המסוגל לתמוך במגוון רחב של מוצרים העונים על דרישות אלו במגוון רחב של יישומי מערכת משובצים קריטיים.

מאמר זה מתאר בקצרה את ההתפתחות של תכנון מערכות משובצות קריטיות. לאחר מכן הוא מציג כיצד ניתן להשתמש במעבדי יישומים רבי-ליבות - שתוכננו במיוחד על ידי חברת NXP Semiconductors לתמיכה ברשימת דרישות המתרחבת במהירות עבור הן פונקציונליות רחבה והן יכולות הרשאת בטיחות - כדי להתמודד עם אתגרי המפתחים.

התפתחות שיקולי התכנון של מערכות משובצות

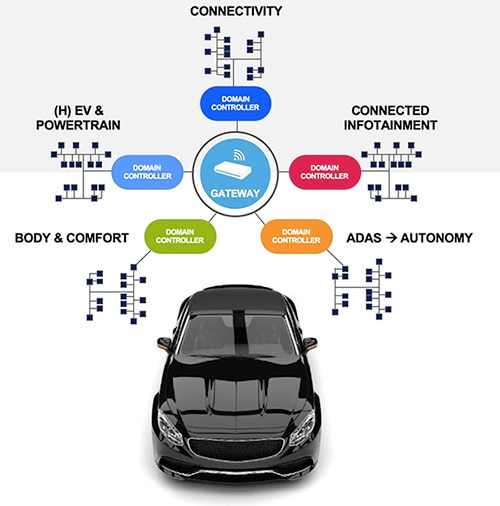

התפקיד המסורתי של התקנים משובצים בתמיכה במערך מוגבל של פונקציות מערכת התחלף במידה רבה לביקוש להתקנים המספקים יכולות רחבות. ביישומים תעשייתיים, כדוגמה, הצורך ביכולות HMI משופרות בכלים ובציוד חכמים מכתיב מעבדים המסוגלים לספק גרפיקה ממוטבת תוך עמידה בדרישות זמן-אמת תעשייתיות מסורתיות יותר. בדומה, המגמה ביישומי כלי-רכב לכיוון של ארכיטקטורות היררכיות הכוללות אשכולות פונקציונליים יצרה את הצורך במעבדים המסוגלים לעמוד בדרישות אלו במלואן (איור 1).

איור 1: המגמה לכיוון של ארכיטקטורות מערכות כלי-רכב היררכיות יותר יצרה את הצורך בפתרונות מעבדים משולבים ומידרגיים יותר. (מקור התמונה: NXP Semiconductors)

איור 1: המגמה לכיוון של ארכיטקטורות מערכות כלי-רכב היררכיות יותר יצרה את הצורך בפתרונות מעבדים משולבים ומידרגיים יותר. (מקור התמונה: NXP Semiconductors)

בתוך כל אשכול פונקציונלי, הביקוש עבור יכולות מתוחכמות יותר ממשיך להעלות את סף הביצועים והיכולות המשולבות. לדוגמה, הופעתן של תצוגות עיליות (HUD) דורשת פתרונות המסוגלים להבטיח רציפות העברת מידע גרפי חיוני לנהגים. לצד תצוגות הדור-הבא, הצורך הגובר במודעות נהג משופרת מוסיף דרישות נוספות עבור ממשקי מצלמה והרצה עם ביצועים עיליים של תוכנות זיהוי מתקדמות המסוגלות לספק זיהוי נמנום.

ככל שהיישומים ממשיכים להתפתח, הצורך בפיתרונות מידרגיים ומשולבים ביותר הופך לדחוף יותר כדי לעמוד בדרישות מגוונות יותר ויותר, תוך הקטנה למינימום של חתימת-השטח, העלות והמורכבות של התכן. באמצעות משפחת מעבדי היישומים i.MX 8 מבית NXP, המפתחים יכולים למנף פלטפורמה תואמת של מעבדים עם מגוון היכולות והביצועים הדרושים לתמיכה במגוון רחב של דרישות יישומים. במסגרת משפחת i.MX 8, סדרת i.MX 8X מבית NXP נותנת מענה לצרכים המתעוררים עבור מעבדים הניתנים להרשאת בטיחות הנדרשים ביישומי כלי-רכב ותעשייה בתחום-הביניים.

ארכיטקטורה רבת-ליבות מנהלת עומסי עבודה מגוונים

אחד הקשיים העומדים בפני מפתחים במימוש יישומים בכלי-רכב ובתעשייה הוא עצם המגוון הרחב של הדרישות. היכן שהמפתחים יכלו לצפות להתמודד עם עומסי עבודה של עיבוד יישומי רמה-גבוהה או זמן-אמת, הביקוש עבור תת-מערכות חכמות מיזג סוגי מחשוב שונים אלו משמעותית. המפתחים זקוקים יותר ויותר לפיתרונות המסוגלים לתת גם היענות אמינה בזמן-אמת וגם הרצת אפליקציות עם ביצועים-עיליים תוך תמיכה בדרישות הבטיחות הפונקציונליות.

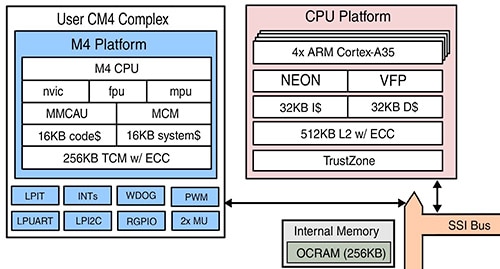

מתוכננים לספק יכולות זמן-אמת, עיבוד עם ביצועים עיליים וצריכת הספק נמוכה, מעבדי סדרת i.MX 8X מבית NXP ומנצלים במלואה את ארכיטקטורת יחידת עיבוד מרכזית (CPU) רבת-ליבות מתוחכמת לניהול עומסי עבודה חישוביים מגוונים (איור 2).

איור 2: סדרת i.MX 8X מבית NXP משתמשת בארכיטקטורה רבת-ליבות הכוללת מעבד משובץ של Cortex-M4 (CM4) מבית Arm ומספר מעבדי יישומים Cortex-A35 מבית Arm לתמיכה בעומסי עבודה של מספר תוכנות שונות. (מקור התמונה: NXP Semiconductors)

איור 2: סדרת i.MX 8X מבית NXP משתמשת בארכיטקטורה רבת-ליבות הכוללת מעבד משובץ של Cortex-M4 (CM4) מבית Arm ומספר מעבדי יישומים Cortex-A35 מבית Arm לתמיכה בעומסי עבודה של מספר תוכנות שונות. (מקור התמונה: NXP Semiconductors)

עבור משימות עיבוד בזמן-אמת למטרות כלליות, התקני i.MX 8X כוללים מעבד Cortex-M4 (CM4) מבית Arm עם יחידת נקודה צפה (FPU), יחידת הגנת זיכרון (MPU), יחידת האצת קריפטוגרפיה ממופה-זיכרון (MMCAU), ומודול בקרה אחר (MCM). לתמיכה ברכיבים היקפיים חיצונים כמו חיישנים ומפעילים (Actuators), הרכב CM4 משתמש זה משלב בקר Nested Vector Interrupt Controller (NVIC) עם סט מקיף של ממשקים ומודולים, כולל קוצב-זמן Low-Power Periodic Interrup Timer (LPIT), אפנון רוחב פולס (PWM), וכן פונקציות אחרות הנדרשות לרוב ביישומי כלי-רכב ותעשייה. זוג זיכרונות Cache וזיכרון Tightly Coupled Memory (TCM) עם יכולת קוד תיקון שגיאות (ECC) מסייעים בהקטנה למינימום של הגישות לזיכרון חיצוני, הרצה מהירה וטיפול בשגיאות זיכרון.

עבור הרצה מהירה של עומסי העבודה של היישומים, פלטפורמת יחידות המעבד המרכזי (CPU) מורכבת ממספר מעבדי יישומים (AP) Arm Cortex-A35 עם נצילות הספק טובה - שני מעבדי יישומים ב- 8DualXPlus כגון ה- MIMX8UX6AVLFZAC, וארבעה מעבדי יישומים ב- 8QuadXPlus כגון ה- MIMX8QX6AVLFZAC. לצד זיכרון Cache ייעודי לפקודות ($I) ולנתונים ($D), פלטפורמת ה- CPU כוללת זיכרון Cache Level 2 (L2) של 512 קילו-בייט (Kbyte) עם ECC.

ליבות Arm Cortex-A35 של הארכיטקטורה מעניקות תאימות תוכנה ומידרגיות ביצועים גם יחד, ותומכות הן בתאימות לאחור של Bit-32 והן בביצועי Bit-64. כדי לזרז עוד יותר את ההרצה של אלגוריתמים עתירי-חישובים כגון עיבוד אותות ולמידת מכונה, מעבדי Arm Cortex-A35 מספקים עיבוד נקודה צפה וקטורי (VFP) והרחבות ארכיטקטורת פקודה-אחת-מספר-נתונים (SIMD) Neon מבית Arm. כדי להאיץ את ההרצה של תוכנות עבור עיבוד תמונות, ראיית מחשב ולמידת מכונה, ספריית Compute Library מבית Arm מציעה פונקציות הממוטבות עבור ארכיטקטורות מעבדים ויחידות עיבוד גרפי (GPU) מבית Arm, וספריית קוד פתוח C Ne10 מספקת פונקציות ממוטבות-Arm עבור פעולות עתירות-מחשוב.

מנועים ייעודיים מורידים את העומס מהמעבדים העיקריים

בנוסף להרכב CM4 משתמש ולפלטפורמת CPU רב-ליבות Arm Cortex-A35, הארכיטקטורה מספקת מנועים ייעודיים נוספים עבור יישומי מולטימדיה. לצד מעבד אותות דיגיטלי (DSP) עבור עיבוד Codec אודיו וקול, הארכיטקטורה משלבת GPU ויחידת עיבוד וידאו (VPU) גם יחד. ה- GPU של ההתקן תומך בספריות גרפיקה סטנדרטית, תוך האצת פעולות באמצעות ארבעה וקטורי נקודה-צפה נפרדים עם ארבעה-רכיבים (vec4) עם 16 יחידות הרצה ומנוע Bit Blit דו-ממדי עם ביצועים עיליים. ה- VPU מטפל בפורמטי וידאו פופולריים, מאיץ פענוח עד 4Kp30 (פרוגרסיבי,Hz 30) וקידוד עד 1080p30. בתורו, בלוק בקר התצוגה הייעודי של השבב יכול לדחוף יציאת גרפיקה לעד שלושה צגים עצמאיים.

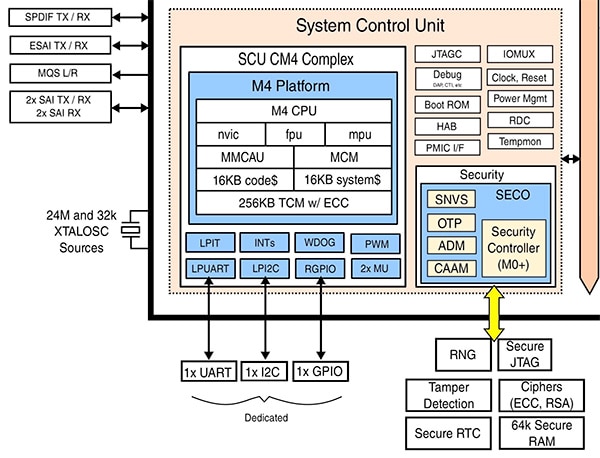

כדי למקסם עוד יותר את הביצועים, ארכיטקטורת i.MX 8X משלבת גם ליבות מעבד נוספות שתוכננו לשחרר את פלטפורמות המעבד העיקריות מעומס העיבוד הנוסף שנוצר בדרך כלל בהרצת שירותי ניהול ואבטחה של המערכת. עבור ניהול המערכת, יחידת בקרת המערכת (SCU) של הארכיטקטורה משלבת הרכב CM4 התואם להרכב CM4 משתמש אך נותר ייעודי לחלוטין לפעולות ה- SCU ואינו זמין לשימוש המפתחים (איור 3).

איור 3: משולבת עמוק בתוך מעבדי i.MX 8X מבית NXP ואינה זמינה למפתחים, יחידת בקרת המערכת (SCU) משתמשת בתת-מערכת Cortex-M4 (CM4) מבית Arm ייעודית כדי להוריד את עומס משימות ניהול המערכת מהמעבדים הראשיים של ההתקן. (מקור התמונה: NXP Semiconductors)

איור 3: משולבת עמוק בתוך מעבדי i.MX 8X מבית NXP ואינה זמינה למפתחים, יחידת בקרת המערכת (SCU) משתמשת בתת-מערכת Cortex-M4 (CM4) מבית Arm ייעודית כדי להוריד את עומס משימות ניהול המערכת מהמעבדים הראשיים של ההתקן. (מקור התמונה: NXP Semiconductors)

לצד ניהול הספקת-הכוח, השעון והפונקציות הפנימיות האחרות, ה- SCU מבקר את ריבוב הפינים ואת חוזק דחיפת ערוצי הכניסה/יציאה (I/O) בפעולה רגילה. למעשה הרכב CM4 משתמש ומעבדי היישומים Arm Cortex-A35 אינם יכולים לגשת ישירות ליכולות חומרה ברמה-הנמוכה מגוונות אלו. במקום זאת, ה- SCU משמש להפשטת יכולות אלה, כך שתוכנה הפועלת על CM4 משתמש או מעבדי יישומים פשוט צריכה לקרוא לפונקציות ממשק תכנות יישומים (API) של קושחת ה- SCU כדי לבצע פונקציות כגון השבתת אשכולות הספקת-כוח לא-נחוצים. לדוגמה, אם אשכול הספקת-כוח משותף עם מעבד אחר, ה- SCU פשוט מאשר את דרישת ההשבתה אך שומר על אשכול הספקת-הכוח מוזן עד שאותו מעבד אחר שולח גם כן דרישת השבתה.

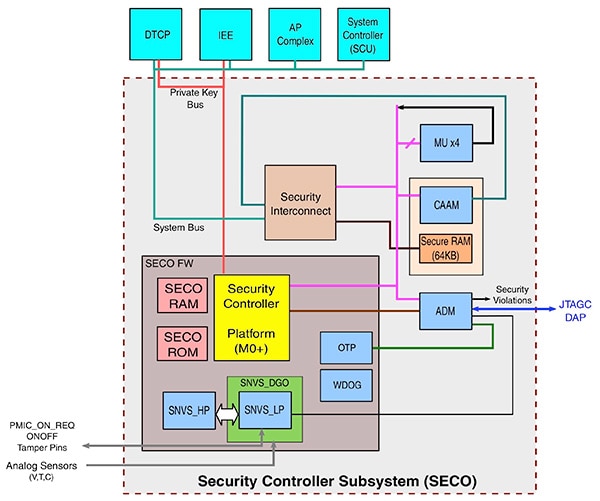

כדי לנהל את תמיכת האבטחה הנרחבת של התקן i.MX 8X, נכנס לתמונה מעבד ייעודי נוסף בתת-מערכת בקר האבטחה (SECO) של ההתקן. בתוך תת-מערכת SECO, מעבד +Arm Cortex-M0 משולב בהספק-נמוך מריץ קושחה התומכת ביכולות אבטחה מבוססות-חומרה, כולל גישת אפיק פרטי עבור מפתחות מאובטחים, זיכרון תכנות חד-פעמי (OTP) עבור אחסון מפתחות מאובטח, ואחסון לא-נדיף מאובטח (SNVS) עבור נתונים פרטיים נוספים או מפתחות מסוג Ephemeral (איור 4).

איור 4: בתוך תת-מערכת SECO i.MX 8X מבית NXP, מעבד +Arm Cortex-M0 ייעודי בהספק-נמוך מנהל את פעולות האבטחה, ומשתמש באפיק מפתחות פרטיים ובמספר מודולי חומרה עבור אחסון מאובטח, האצת קריפטוגרפיה וגישת ניפוי-באגים מאומתת. (מקור התמונה: NXP Semiconductors)

איור 4: בתוך תת-מערכת SECO i.MX 8X מבית NXP, מעבד +Arm Cortex-M0 ייעודי בהספק-נמוך מנהל את פעולות האבטחה, ומשתמש באפיק מפתחות פרטיים ובמספר מודולי חומרה עבור אחסון מאובטח, האצת קריפטוגרפיה וגישת ניפוי-באגים מאומתת. (מקור התמונה: NXP Semiconductors)

מעבר למנגנוני אבטחה מרכזיים אלה, תת-מערכת SECO מתאמת פעולות אבטחה לגילוי השחתה וניפוי-באגים מאובטח המתווך באמצעות מודול ניפוי-באגים מאומת (ADM) שלה. לצורך הרצה מאובטחת, מודול האבטחה בחומרה של מודול האצת והבטחת קריפטוגרפיה (CAAM) תומך במערך שלם של אלגוריתמי אבטחה הכוללים הצפנה סימטרית ואסימטרית, פונקציות Hash ומחולל מספרים אקראיים (RNG).

בפעולה רגילה, יחידות העיבוד של ההתקן הכוללות SCU, מעבדי יישומים ומאיץ Digital Transport Content Protection (DTCP) משתמשות בחיברורי הבטיחות SECO לגישה לפונקציונליות CAAM דרך אפיק המערכת. פרט לגישה באמצעות פונקציונליות גישה ישירה לזיכרון (DMA), מעבד +Cortex-M0 הייעודי של ה- SECO אינו יכול לגשת לאפיק המערכת. במקום זאת, הוא משתמש בחיבורים פנימיים מוגנים לגישה לרכיבים היקפיים, לזיכרון גישה אקראית (RAM) מאובטח, לזיכרון קריאה-בלבד (ROM) ולאפיק המפתחות הפרטיים המיוחד שלו.

לצד השימוש שלו במאיץ DTCP, אפיק מפתחות פרטיים זה ממלא תפקיד מרכזי בתמיכה במעבד i.MX 8X עבור הצפנה ופענוח תוך-כדי-פעולה. כאן, מעבד האבטחה משתמש במשאביו כדי לספק את המפתחות הפרטיים הדרושים למודול מנוע הצפנה/פענוח בקו-אחד (IEE) של ההתקן בזמן שהוא קורא או כותב באופן מאובטח מ/ל-תוך אחסון מוצפן, ללא מעורבות של המעבד המבקש, בקר DMA או התקן I/O.

על בסיס טכנולוגיית TrustZone מבית Arm המשולבת במעבדי Cortex-A35 של ההתקן, תת-מערכת SECO עובדת גם עם ה- SCU במהלך תהליך האתחול (Boot) המאובטח. בתהליך זה, ה- SCU מפרש את הגדרות האתחול, מגדיר את מקורות האתחול, וטוען את תמונת האתחול לזיכרון פנימי או חיצוני. בתורה, תת-מערכת SECO משתמשת בפונקציות ההצפנה שלה כדי לאמת תמונות קושחה חתומות לאחר טעינתן אך לפני הרצתן.

הגנה על תצוגות קריטיות ופונקציונליות בקרה

בעוד שהיכולת לעבד עומסי עבודה מגוונים ביעילות ובאופן מאובטח היא חשובה, עבור יישומים קריטיים למשימות כמו אלה במגזרי כלי-רכב ותעשייה, היכולת להגן על יכולות מפתח היא חיונית באותה מידה. משפחת i.MX 8X מבית NXP משלבת את יכולות העיבוד שלה עם יכולות ניתנות להרשאת בטיחות הנדרשות כדי לעמוד בדרישות קריטיות אלו.

תמיכת הבטיחות של משפחת המעבדים מובנית במספר רמות, החל מייצור בטכנולוגיית תהליךFully Depleted Silicon-On-Insulator (FD-SOI) המשפרת את אמינות המערכת. מאחר שבטיחות המערכת תלויה ביסודות אבטחה חסונים, השילוב של מעבדי יישומים מאופשרי-TrustZone, תת-מערכת SECO ויכולות אתחול (Boot) מאובטח יכול לספק את הסביבה המהימנה הדרושה כדי לסכל איומים על הבטיחות והביטחון.

יחד עם זאת, היכולת לטפל באופן עצמאי במשימות קריטיות-בזמן עם הרכב CM4 משתמש ולהוריד משימות מערכת קריטיות לתת-המערכות SCU ו- SECO מסייעת להבטיח שיכולות יישום קריטיות-למשימות יישארו זמינות למרות עומס העיבוד המשתנה. למעשה, חברת NXP מרחיבה את הרעיון הזה לתמיכה עבור תצוגות קריטיות-למשימות באמצעות טכנולוגיית SafeAssure של החברה, המשלבת מסלול יתירות-כשל (Failover)לתצוגות החומרה מוכני-Automotive Safety Integrity Level B (ASIL B) שבהתקני i.MX 8X. באמצעות SafeAssure, למשתמשים מסופקת אוטומטית תמונת יתירות-כשל (Failover) אם ההתקן מזהה תקינות נתונים או שגיאת GPU. רצה ברקע, תמונת יתירות-כשל (Failover) מבטיחה שהנתונים הקריטיים נותרים זמינים אפילו במהלך תקלה של התצוגה העיקרית.

התמיכה ביישומי בטיחות מתרחבת לגישה לזיכרון במערכות מבוססות i.MX 8X. בין ממשקי הזיכרון הנתמכים שלהם, התקני i.MX 8X מספקים ECC Bit-8 עבור זיכרון קצב נתונים כפול 3 במתח נמוך (DDR3L). לצד ECC ב- L2 Cache (ראו שוב איור 2), יכולת ECC DDR3L זו תומכת ב- Safety Integrity Level 3 (SIL 3) תעשייתי. ארכיטקטורת i.MX 8X מרחיבה את תמיכת ECC גם להתקני אחסון Flash חיצוניים. כאן, מודול מקודד ומפענח Bose, Ray-Chaudhuri, Hocquenghem (BCH) משולב מספק ECC Bit-62 היכול לתקן 2 עד 20 שגיאות ביט-יחיד בתוך בלוק של נתונים הנקראים מתוך התקני אחסון אלו.

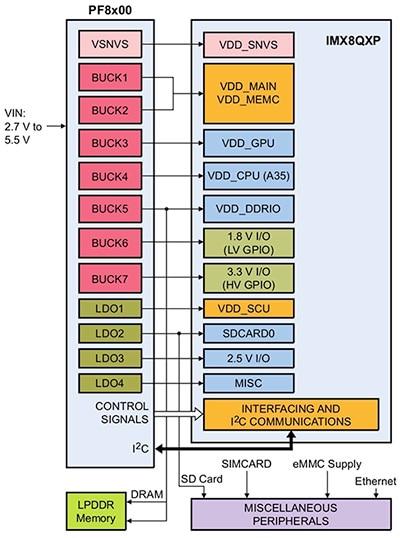

התנעת יישומים מבוססי-i.MX 8X

כמו עם כל מעבד בקטגוריה זו, יישום תכן מבוסס-i.MX 8X דורש התייחסות זהירה לדרישות המחמירות עבור הספקת-הכוח, כולל רצפי הפעלה ראשונית קריטיים. הפעלה ראשונית של התקני i.MX 8X דורשת העלאה הדרגתית של ההספק ברצף או בו-זמנית לארבע קבוצות הספקת-כוח שונות, החל מתת-מערכת SVNS והמשך עם SCU, ממשקי ה- I/O והזיכרון, ולבסוף את יתר ההתקן. המפתחים יכולים לעמוד בדרישה זו פשוט באמצעות התקני מעגלים-משולבים לניהול הספקת-כוח (PMIC) PF8x00 מבית NXP, המספקים מערך שלם של פסי מתח ואותות בקרה הדרושים לתמיכה במעבדי i.MX 8X, כמו גם בזיכרון חיצוני וברכיבים היקפיים טיפוסיים למערכת (איור 5).

איור 5: רכיבי PF8x00 PMIC מבית NXP מספקים מערך שלם של פסי מתח ואותות בקרה הנחוצים עבור הספקת-הכוח למעבדי i.MX 8X. (מקור התמונה: NXP Semiconductors)

איור 5: רכיבי PF8x00 PMIC מבית NXP מספקים מערך שלם של פסי מתח ואותות בקרה הנחוצים עבור הספקת-הכוח למעבדי i.MX 8X. (מקור התמונה: NXP Semiconductors)

במימוש התכנים מבוססי-i.MX 8X משלהם, המפתחים יכולים להשתמש ב- PMIC MC33PF8100CCES מבית NXP המתוכנת-מראש לשימוש עם מעבדי 8QuadXPlus כגון ה- MIMX8QX6AVLFZAC. גרסות PF8x00 אחרות כגון ה- MC33PF8100A0ES ו- MC33PF8200A0ES תומכים במעבדי i.MX 8X אך הם אינם מתוכנתים-מראש.

עבור יישומי בטיחות, התקני סדרת PF8200 כגון ה- MC33PF8200A0ES מאפיינים המתוכננים לתמיכה במערכות ASIL B. לצד מספר מנטרים פנימיים כולל מנטר מתח יציאה עם ייחוס Bandgap ייעודי, רכיבי PF8200 PMIC כוללים פין יציאת אל-כשל (FSOB) המתוכנן לשמור על המערכת במצב בטוח במהלך הפעלה ראשונית או במהלך אירוע תקלה בהספקת-הכוח. בנוסף, רוטינת בדיקה-עצמית אנלוגית מובנית (ABIST) בודקת את כל מנטרי המתח בעוד שרוטינת בדיקה-עצמית מאמתת פונקציונליות אחרת של ההתקן.

אף על פי שרכיבי PF8x00 PMIC יכולות לפשט את תכנון החומרה של מערכות מבוססות i.MX 8X, יתכן שמפתחים מסוימים יצטרכו להתחיל מיד בהערכת התקני i.MX 8X ולבנות במהירות אב-טיפוס של יישומים מבוססי i.MX 8X. ערכת אפשור רבת-חיישנים (MEK) i.MX 8X MCIMX8QXP-CPU מבית NXP מספקת פלטפורמת פיתוח מוכנה המשלבת מעבד 8QuadXPlus i.MX מבית NXP, PMIC F8100 מבית NXP, זיכרון RAM של 3 גיגה-בייט (Gbyte), זיכרון embedded Multi-Media Controller (eMMC) של Gbyte 32, וזיכרון Flash של 64 מגה-בייט (Mbyte). ביחד עם ממשקי צג, מצלמה ואודיו, לוח MEK כולל מערך חיישנים המשמש לרוב ביישומי כלי-רכב או תעשייה. עבור אפשרויות נוספות של חיבוריות, אודיו והרחבות, המפתחים יכולים להוסיף גם את לוח-הבסיס האופציונלי MCIMX8-8X-BB מבית NXP.

סיכום

עבור מספר הולך וגדל של יישומים כגון כלי-רכב, תעשייה, בקרת מבנים ו- HMI, עומסי עבודות העיבוד התרחבו והם כוללים גם עיבוד I/O מסורתי בזמן-אמת וגם עיבוד ברמת יישומים מתפתחים עם גרפיקת מולטימדיה. למרות שקיימות אפשרויות תכנון עבור כל סוג של עומס עבודה, מעטים הפתרונות הזמינים העונים לצורך הגובר בפתרונות יעילי הספק ועם ביצועים עיליים המסוגלים לעמוד בדרישות עבור תכנים ניתנים להרשאת בטיחות ביישומי כלי-רכב ותעשייה.

כפי שהוצג, באמצעות המשפחה של מעבדים רבי-ליבות מבית NXP Semiconductors, המפתחים יכולים לממש בצורה יעילה יותר תכנים המסוגלים לעמוד בדרישות המגוונות הללו ולהתאים אותם בקלות כדי לענות לדרישות המתפתחות עבור ביצועים עיליים.

מיאון אחריות: דעות, אמונות ונקודות מבט המובעות על ידי מחברים שונים ו/או משתתפי פורום באתר אינטרנט זה לא בהכרח משקפות את הדעות, האמונות ונקודות המבט של חברת DigiKey או את המדיניות הרשמית של חברת DigiKey.