הפק תועלת מ-I3C עבור תקשורת IC-ל-IC מהירה יותר, פשוטה יותר וגמישה יותר

באדיבות ‎DigiKey's North American Editors

2024-12-17

ממשקים טוריים על לוח עבור תקשורת מעגל משולב (IC)-ל-IC נשלטים על ידי ה-Inter-Integrated Circuit (I²C) והממשק ההיקפי הטורי (SPI), שזמינים מאז שנות השמונים. ממשקים אלה משמשים באופן נרחב עבור חיבור חיישנים ו-ICs בעלי מהירות נמוכה יותר ליחידות מיקרו-בקר (MCUs) עבור תקשורת בין לוחות למרחקים קצרים. עם זאת, מאחר ומערכות דיגיטליות הופכות למהירות יותר, ממשקים אלה המוגבלים לקצבי נתונים אופייניים של 1 מגה-ביט לשנייה (Mbit/s) עבור I²C ו-10 Mbits/s עבור SPI, הפכו לגורם מגביל. מגבלות אחרות, כולל פסק (Interrupt) ייעודי או קווי אפשור שבב, שדורשים חיבורי אותות נוספים, מגדילים את מספר החוטים ואת המורכבות של חיבורי האפיק.

אפיק ה-Improved Inter-Integrated Circuit (I3C) מיועד לשדרג תקשורת בין מעגלים משולבים. הוא מציע קצבי נתונים גבוהים יותר, גמישות גדולה יותר, וממשק שני חוטים אמיתי עם פסקים (Interrupts) בתוך הפס (IBIs) במקום חיצוניים.

מאמר זה דן במאפיינים של ממשק ה-I3C ומדוע הוא עשוי להיות שדרוג טוב ל-I²C וממשקים טוריים SPI. התקני MCU, מתג IC וחיישן אופייניים ישמשו כדי להראות את היישום שלו.

אפיקי תקשורת משובצים

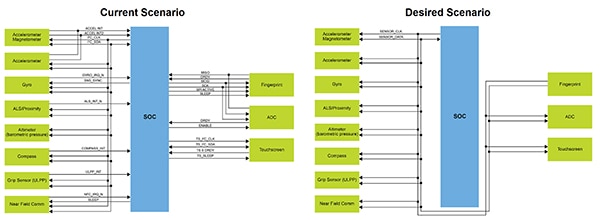

חיבורים טוריים משובצים כמו I²C ו-SPI שמשו במשך שנים רבות עבור תקשורת בין לוחות. הם משמשים בעיקר כאפיקי תקשורת בין חיישנים והתקני ממשק משתמש ומעבדי הבקרה שלהם. מספר החיישנים במערכות אופייניות גדל עד עשרה ועשרים בטלפון ומשמעותית יותר בכלי רכב. במקביל, דרישות התקשורת הפכו להיות מאתגרות יותר למתכננים עם הגידול בדרישות למהירות גבוהה יותר, צריכת הספק נמוכה יותר ופחות מוליכים. מתכננים חייבים לעמוד בדרישות אלו תוך כדי שמירה על בקרת מעבד באמצעות פסקים (Interrupts) וקווי אפשור (איור 1).

איור 1: תקשורת משובצת אמורה לתמוך במהירויות גבוהות יותר, הספק נמוך יותר ומספר חוטים מינימלי. (מקור תמונה: NXP Semiconductors)

איור 1: תקשורת משובצת אמורה לתמוך במהירויות גבוהות יותר, הספק נמוך יותר ומספר חוטים מינימלי. (מקור תמונה: NXP Semiconductors)

הטכנולוגיה הנוכחית מיישמת את ממשק החיישן והתקן בקרת המשתמש על ידי שימוש ב-I²C שני-חוטים או ממשק SPI ארבעה-חוטים. פסק, אפשור וקווי בקרה אחרים הם נפרדים מקווי השעון והנתונים, והתוצאה היא יותר קווים לממשק.

מתכננים צריכים ממשק צופה פני עתיד יותר שאינו דורש מהחברור מוליכים נוספים אלה ומטפל באותן פעולות בתוך-הפס על ידי שימוש בקווי נתונים ושעון בלבד. נוסף לכך, האפיק חייב להיות מסוגל לפעול במהירויות גבוהות יותר ועם הפסדי הספק נמוכים יותר.

ממשק I3C

ה-I3C פותח על ידי ה-Mobile Industry Processor Interface (MIPI) Alliance כדי לענות על דרישות אלו. הממשק זמין כ-MIPI I3C לחברי MIPI, וכ-MIPI I3C Basic עם פונקציונליות פחותה ללא-חברים. כמו הממשקים הישנים I²C ו-SPI, הצורה המשופרת היא טורית ומיושמת על ידי שימוש בשני חוטים כדי להקטין למינימום מספרי פינים ואת מספר מסלולי האותות בין רכיבים. יש לו קצב נתונים של עד 12.5 Mbits/s עם שעון של 12.5 מגה-הרץ (MHz) ומשתמש בשיטת פעולה קצב נתונים יחיד (single data rate (SDR)). הוא עובד ברמות הספק נמוכות יותר ומשתמש בארכיטקטורת תכן פשוטה אך גמישה.

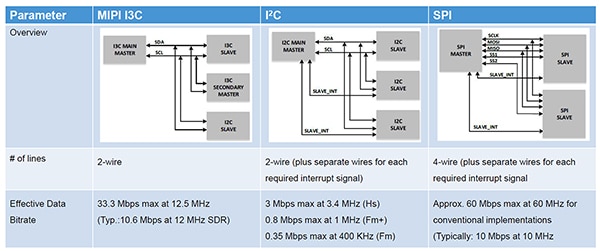

ראוי לציין, תקן ה-I3C שומר על תאימות-לאחור מוגבלת עם מערכת ה-I²C, מאפשר להתקני I²C קיימים להיות מחוברים לאפיק ה-I3C, תוך מתן אפשרות לאפיק לעבור לקצבי נתונים גבוהים יותר עבור תקשורת בין התקני I3C תואמים. השוואה בין תצורות המערכות מוצגת באיור 2.

איור 2: השוואת התצורות הבסיסיות של ממשקי I3C, I²C ו-SPI מראה את המהירות המשופרת והחיווט הפשוט יותר של I3C. (מקור תמונה: NXP Semiconductors)

איור 2: השוואת התצורות הבסיסיות של ממשקי I3C, I²C ו-SPI מראה את המהירות המשופרת והחיווט הפשוט יותר של I3C. (מקור תמונה: NXP Semiconductors)

ממשק ה-SPI ארבעה-חוטים יכול לפעול מהר יותר ותומך בתקשורת דופלקס מלא. I²C מתקשר תוך שימוש בחצי דופלקס דרך אפיק שני-חוטים הכולל קו שעון (SCL) וקו נתונים (SDA). שניהם דורשים קווים נוספים כדי לתמוך בפסקים (Interrupts) ובפונקציות בקרה אחרות כמו בחירת שבב (chip select). ה-I3C מקטין את מספר החוטים שבשימוש הממשק לשניים, מבטל את הצורך בקוי פסק, אפשור ובחירת שבב נפרדים המשמשים ב-I²C ו-SPI. הקטנת מספר חוטים זו היא יתרון משמעותי במערכת הדורשת עשרה עד עשרים חיישנים בדידים מחוברים למעבד, כל אחד עם מספר חוטים משניים. פסקים וקווי בקרה אחרים מוחלפים על ידי IBIs. בשיטה זו, חיישן או התקן מטרה כופה את כתובתו בכותרת כתובת אפיק ה-I3C כדי להודיע למעבד על פסק.

ההבדל בין קצבי השעון של I²C ו-I3C הוא משמעותי. קצב שעון ה-I²C הוא בדרך כלל 100 קילו-הרץ (kHz), 400 kHz או 1 MHz, בעוד קצב השעון של I3C הוא 12.5 MHz. בעבר, SPI שימש עבור קצבי שעון גבוהים מ-1 MHz. בחירת התכנון הייתה בין קצב השעון ומספר החוטים. I3C שינה את זה על ידי הצעת קצבי שעון ונתונים גבוהים יותר תוך שימוש בטופולוגיית שני-חוטים אמיתית.

יציאות Push-Pull, שיכולות להתמתג מהר יותר מדוחפי קולט או שפך-פתוח, תורמות משמעותיות לקצב השעון המוגדל של ה-I3C. כדי לשמור על תאימות עם התקני I²C, I3C יכול להחליף בין דוחפי שפך-פתוח ו-Push-Pull בהתאם למצב האפיק. תכנון קולט או שפך-פתוח משמש במהלך פנייה ראשונית או בוררות, כשהתקני I²C ו-I3C יכולים להיות על הקו בו-זמנית. I3C משתמש ב-Push-Pull כשהתקשורת היא חד-כיוונית, ואין סיכוי שהתקן I²C יתקשר בו-זמנית.

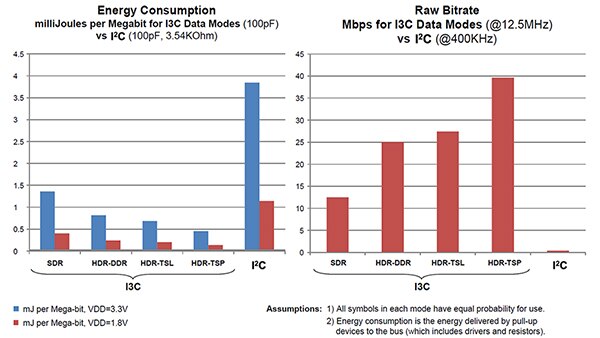

בנוסף ל-SDR הסטנדרטי, I3C תומך במספר שיטות קצב נתונים גבוה (HDR) אופציונליות. שיטות HDR אלו עובדות עם אותו קצב שעון אך משדרות עם צפיפות נתונים גבוהה יותר. הראשונה בין שיטות ה-HDR היא HDR קצב נתונים כפול (HDR-DDR), בה הנתונים מופעלים בשני קצוות אות השעון, ובכך מקבלים כמעט קצב נתונים כפול. במקרה של שעון של 12.5 MHz, שיטת DDR משיגה קצב נתונים אפקטיבי של 20 Mbits/s.

לסמלים טרינריים (ternary symbols) HDR יש שתי גרסאות: סמל טרינרי HDR טהור (HDR-TSP) עבור התקני I3C בלבד, וסמל טרינרי HDR מדור קודם (HDR-TSL) עבור אפיקים הכוללים התקני I²C ו-I3C גם יחד. שיטות סמל טרינרי משיגות שלושה ביטים של נתונים לאות שעון תוך שימוש בסמלי שלושה ביטים (טרינרי) מקודדים על קווי ה-SDL ו-SDA.

שיטת HDR bulk transport (HDR-BT) מציעה את הנתונים הגבוהים ביותר על ידי תמיכה בתקשורת דרך ארבעה חוטי נתונים SDA, שניים או חוט יחיד. התוצאה של זה היא ביצועי קצב נתונים גולמי פי שמונה, ארבעה או שניים באותו קצב שעון.

עליות אלה במהירות העברת הנתונים מאפשרות הפעלת התקנים לתקופה קצרה יותר, מקצרות את מחזור הפעולה (duty cycle) הצורך הספק של האפיק. זה מקטין צריכת הספק בהשוואה ל-I²C (איור 3). השינוי מדוחפי קולט-פתוח (OC) עם נגדי pull-up חיצוניים לדוחפי Push-Pull מצמצמים עוד יותר את צריכת ההספק, מאחר ונגדי pull-up דורשים הספק משמעותי כדי לעבוד.

איור 3: I3C מציע שיפורים בקצב נתונים וצריכת הספק בהשוואה ל-I²C (מקור תמונה: NXP Semiconductors)

איור 3: I3C מציע שיפורים בקצב נתונים וצריכת הספק בהשוואה ל-I²C (מקור תמונה: NXP Semiconductors)

מיעון

I²C משתמש בכתובות סטטיות באורך 7 או bit-10 עבור כל התקן אפיק. זה שונה ב-I3C למיעון דינמי של 7-bit, כש-Master האפיק קובע את כתובת ההתקן במהלך הקצאת כתובת דינמית (DAA), ומאחסן אותה באוגר התקן (device register). מיעון סטטי, כמו במקרה של I²C היקפי, יכול עדיין לשמש ב-I3C.

הודות למיעון דינמי, כתובות התקן ניתנות לשינוי מאוחר יותר. זה תומך בהצטרפות חמה, שמאפשרת הוספת התקן חדש לאפיק בעוד הוא עובד. ההתקן החדש, המחובר לאפיק ה-I3C, מאותת על נוכחותו ל-I3C Master על ידי שליחת בקשת הצטרפות חמה. בקר ה-Master מאשר את הבקשה ומקצה כתובת כדי להוסיף את ההתקן לאפיק.

IBIs

ה-I3C הוא אפיק שני-חוטים אמיתי המשתמש ב-IBIs במקום קווי פסקים ייעודיים כמו ה-I²C. ה-IBIs מתרחשים כשהתקן מטרה מאותת את זמינותו ל-Master על ידי משיכה מטה של קו ה-SDA. אחר כך ה-Master מפעיל את השעון על קו ה-SCL, והתקן המטרה משדר את כתובתו על אפיק ה-I3C כדי להודיע לבקר על פסק.

קודים נפוצים של פקודות

קודים נפוצים של פקודות (CCC) הם פקודות סטנדרטיות שהבקר יכול לשדר כשידור כללי לכל התקני ה-I3C בו-זמנית או להתקן מטרה ספציפי. פקודות אלו הן בנושאים הקשורים לניהול אפיק. פורמט פרוטוקול ה-CCC מתחיל עם כתובת השידור של ה-I3C, שמזוהה על ידי כל התקני ה-I3C על האפיק. אף התקן I²C על האפיק לא יאשר את הבקשה מכיוון שזו כתובת I²C מוסתרת.

כל פקודה כוללת שדה מזהה מתאר של 8-bit ואחריו יכול לבוא תוכן פקודה. פקודה הנשלחת להתקן ספציפי מעבירה את כתובת ההתקן בבייט הראשון של התוכן. ישנן יותר מארבעים פקודות CCC, כולל:

- Enter Dynamic Address Assignment (ENTDAA)

- Set New Dynamic Address Assignment (SETNEWDA)

- Enable Events (ENEC)/Disable Events (DISEC)

- Reset Dynamic Address Assignment (RSTDAA)

- Enter High Data Rate Mode (ENTHDRx)

- Get Device Characteristics Register (GETDCR)

לספקים מותר להשתמש במגוון ייעודי של מזהי CCC כדי לממש את הפקודות שלהם.

זיהוי שגיאות ושחזור

שלא כמו I²C, I3C כולל אמצעים לזיהוי שגיאות ושחזור. שש שיטות שגיאה ושחזור עבור התקני יעד הן חובה, ואחת אחרת היא אופציונלית. שיטות שגיאה ושחזור נוספות זמינות גם כן במיוחד עבור שגיאות בצד ה-Master.

רכיבים נתמכים I3C

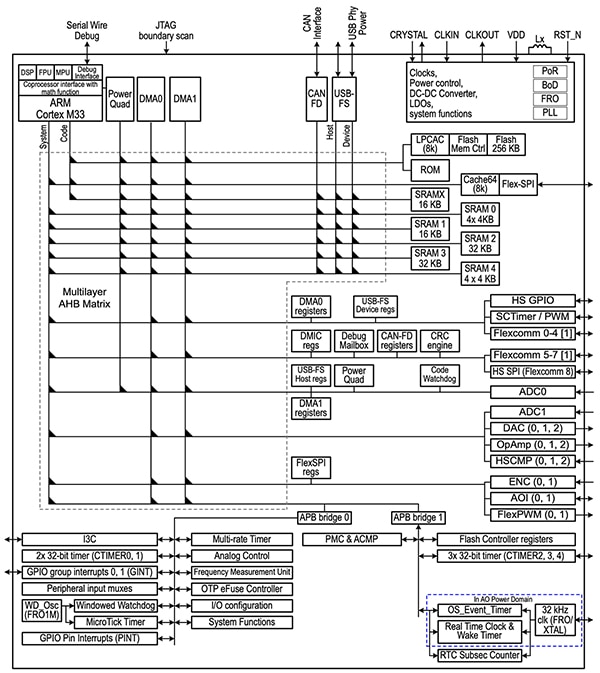

כמתואר באיור 2 (שמאל), רשת I3C בסיסית כוללת לפחות בקר Master אחד ואחת או יותר מטרות I3C, או Slaves. ה-Master העיקרי יכולה להיות יחידת מיקרו-בקר (MCU) כמו ה-NXP Semiconductors LPC5534JHI48-00MP (איור 4). זוהי 32-bit Arm® Cortex®-M33 MCU עם 128 קילו-בייט (Kbytes) של SRAM ו-256 קילו-בייט של Flash. ממשק ה-Flexcomm שלה תומך בשמונה ממשקים טוריים שונים, כולל I3C.

איור 4: ה-LPC5534JHI48/00MP MCU כוללת ממשק I3C ושבעה ממשקים טוריים אחרים. (מקור התמונה: NXP Semiconductor)

איור 4: ה-LPC5534JHI48/00MP MCU כוללת ממשק I3C ושבעה ממשקים טוריים אחרים. (מקור התמונה: NXP Semiconductor)

אפיק ה-I3C מאפשר את ההוספה של Masters שניוניים המוצגים לאפיק כ-Slaves. ל-I3C יכולים להיות Masters מרובים, אך רק אחד יכול להיות הבקר. ברגע שנרשם, ה-Master השניוני יכול לבקש את סטטוס ה-Master הנוכחי, ואם ה-Master הנוכחי מסכים, השליטה שלו עוברת ל-Master המבקש השניוני.

חיישן I3C אופייני הוא P3T2030CUKAZ של NXP. חיישן טמפרטורה זה ממיר טמפרטורות מ-40°C- עד 125°C+ לערך ספרתי של 12-bit עם דיוק של ±2°C. הוא כולל ממשק טורי בשיטת I3C SDR כמו גם I²C.

חיישן מתוחכם יותר הוא הג'ירוסקופ ומד-התאוצה מערכות מיקרו-אלקטרו-מכניות (MEMS) שלושה צירים ICM-42605 מבית TDK InvenSense. כג'יירו קצב, הוא מודד קצבי סיבוב מ-±15.2 עד ±2000 מעלות לשנייה (s/°). התחום שלו כמד תאוצה הוא ±2 עד ±15 g. הוא מגלה תנועה, נטייה, tap או צעדים (מד צעדים). כחיישן I3C, הוא עובד ב-12.5 MHz בשיטת SDR ו-25 MHz בשיטת DDR.

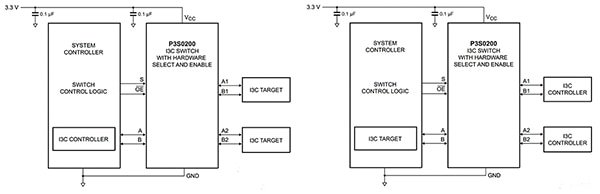

ICs כמו מתג ה-NXP P3S0200GMX I3C יכולים לשנות תצורה של אפיק ה-I3C על ידי ניתוב אותות אפיק I3C בין בקר I3C וסטים מרובים של התקני מטרה, או בין מטרה יחידה ובקרי I3C מרובים, כפי שנקבע על ידי MCU חיצוני (איור 5).

איור 5: מתג ה-P3S0200GMX I3C יכול לשמש לשנות תצורה של אפיק I3C על ידי ניתוב אותות אפיק I3C בין בקר I3C וסטים מרובים של התקני מטרה, או בין מטרה יחידה ובקרי I3C מרובים. (מקור תמונה: NXP Semiconductors)

איור 5: מתג ה-P3S0200GMX I3C יכול לשמש לשנות תצורה של אפיק I3C על ידי ניתוב אותות אפיק I3C בין בקר I3C וסטים מרובים של התקני מטרה, או בין מטרה יחידה ובקרי I3C מרובים. (מקור תמונה: NXP Semiconductors)

יכול להיות צורך במיתוג בין שתי מטרות אם לשתי המטרות יש אותה כתובת ואינן יכולות להיות על אותו אפיק. לחלופין, ייתכן שיהיה צורך לשתף מטרה יחידה בין שני תהליכים, דבר הדורש מתג בין שני בקרי ה-I3C.

סיכום

I3C הוא ממשק טורי המרחיב את אפיק ה-I²C על ידי הגדלת קצב הנתונים שלו, הפחתת מספר החוטים והוספת גמישות לבקרת האפיק. זהו שיפור המרחיב את השימושיות של ממשקי I²C ו-SPI מדור קודם.

מיאון אחריות: דעות, אמונות ונקודות מבט המובעות על ידי מחברים שונים ו/או משתתפי פורום באתר אינטרנט זה לא בהכרח משקפות את הדעות, האמונות ונקודות המבט של חברת DigiKey או את המדיניות הרשמית של חברת DigiKey.