השתמשו בנתיב המהיר של FPGA לבניית יישומי AI-קצה עם ביצועים עיליים ונצילות הספק טובה

באדיבות ‎DigiKey's North American Editors

2021-01-12

מתכננים המבקשים לממש אלגוריתמי בינה מלאכותית (AI) על מעבדי היסק בקצה הם תחת לחץ קבוע להוריד את צריכת ההספק ולקצר את זמן הפיתוח, אפילו כאשר דרישות העיבוד גדלות. מערכי שערים ניתנים לתכנות בשטח (FPGA) מציעים שילוב יעיל במיוחד של מהירות ונצילות הספק עבור מימוש של מנועי היסק רשת נוירונית (NN) הנדרשים עבור AI קצה. עם זאת, עבור מפתחים שאינם מכירים FPGA, שיטות פיתוח FPGA קונבנציונליות יכולות להיראות מורכבות, ולעתים קרובות לגרום למפתחים לפנות לפתרונות פחות אופטימליים.

מאמר זה מתאר גישה פשוטה יותר מבית Microchip Technology המאפשרת למפתחים לעקוף את פיתוח ה- FPGA המסורתי כדי ליצור רכיבי NN מאומנים באמצעות רכיבי FPGA וערכת פיתוח תוכנה (SDK), או להשתמש בערכת וידאו מבוססת-FPGA כדי לעבור מיד לפיתוח יישומי ראייה משובצים חכמים.

מדוע להשתמש ב- AI בקצה?

מחשוב קצה מביא מספר יתרונות ליישומי אינטרנט של דברים (IoT) בסגמנטים שונים כמו אוטומציה תעשייתית, מערכות אבטחה, בתים חכמים ועוד. ביישומי IoT תעשייתי (IIoT) המיועדים עבור רצפת הייצור, מחשוב קצה יכול לשפר דרמטית את זמן התגובה בחוגי בקרת תהליכים על ידי ביטול השיהויים הלוך-וחזור ליישומים מבוססי-ענן. באופן דומה, מערכת אבטחה מבוססת-קצה או מנעול דלת בית חכם יכולים להמשיך ולתפקד גם כאשר החיבור לענן אבד לא-בכוונה או במכוון. במקרים רבים, שימוש במחשוב קצה בכל אחד מיישומים אלה יכול לסייע בהורדת עלות התפעול הכוללת על ידי צמצום התלות של המוצר במשאבי הענן. במקום להתמודד עם צורך בלתי צפוי במשאבי ענן יקרים נוספים ככל שהביקוש למוצריהם גדל, המפתחים יכולים להסתמך על יכולות עיבוד מקומיות המובנות במוצריהם כדי לסייע בשמירה על הוצאות תפעול יציבות יותר.

האימוץ המהיר והביקוש המוגבר למודלי היסק של למידת מכונה (ML) מעצימים דרמטית את חשיבות מחשוב הקצה. עבור מפתחים, עיבוד מקומי של מודלי היסק מסייע בקיצור שיהוי התגובה והפחתת עלויות משאבי הענן הנדרשים עבור היסק מבוסס-ענן. עבור המשתמשים, השימוש במודלי היסק מקומיים מוסיף את הביטחון שהמוצרים שלהם ימשיכו לתפקד למרות איבוד אקראי של החיבוריות לאינטרנט או שינויים בהיצע מבוסס-הענן של ספק המוצר. בנוסף, חששות לגבי אבטחה ופרטיות יכולים לדחוף עוד יותר את הצורך בעיבוד ובהיסק מקומיים כדי להגביל את כמות המידע הרגיש המועבר לענן דרך האינטרנט הציבורי.

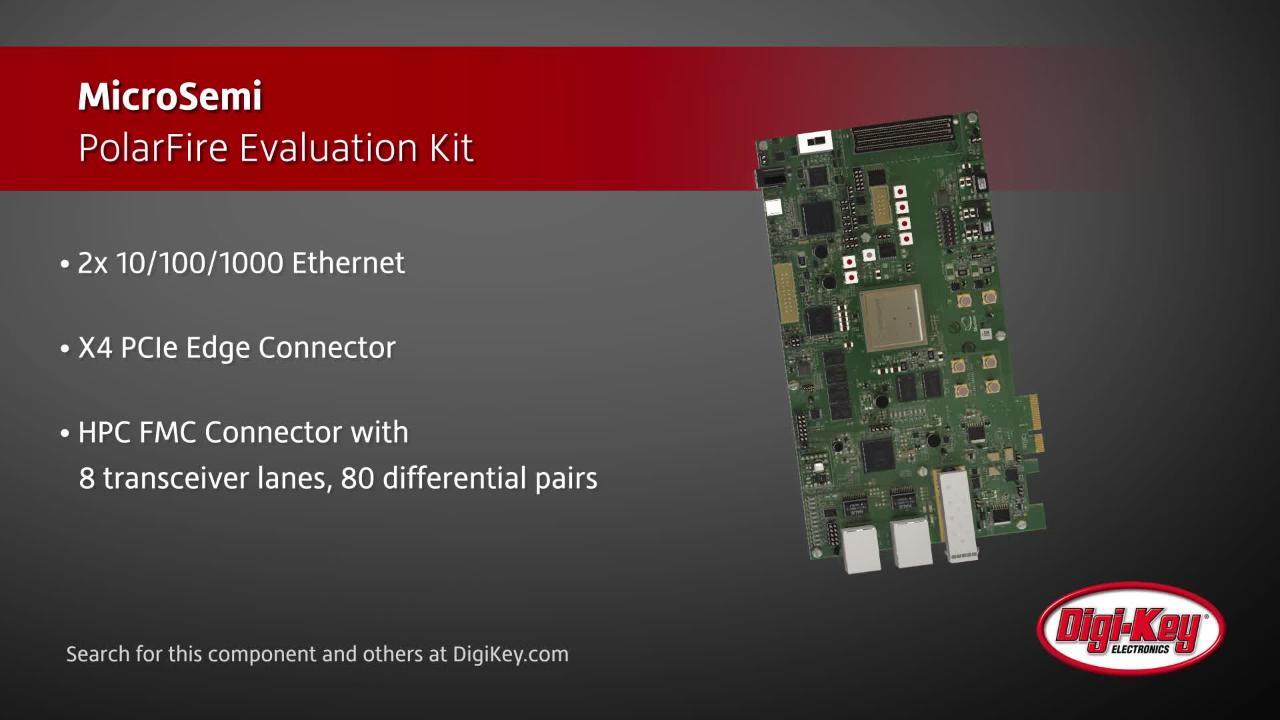

פיתוח מודל היסק NN לגילוי אובייקטים מבוסס-ראייה הוא תהליך רב-שלבי המתחיל באימון המודלים, המבוצע בדרך כלל על מסגרת-עבודה ML כגון TensorFlow תוך שימוש בתמונות עם תוויות זמינות בפומבי או בתוויות מותאמות-במיוחד. עקב דרישות העיבוד, אימון המודלים מבוצע בדרך כלל עם יחידות עיבוד גרפי (GPU) בענן או בפלטפורמת מחשוב אחרת עם ביצועים עיליים. לאחר השלמת האימון, המודל מומר למודל היסק המסוגל לפעול על משאבי מחשוב קצה או מחשוב ערפל, ולספק את תוצאות ההיסק כמערך של הסתברויות Object Class (איור 1).

איור 1: מימוש מודל היסק עבור AI קצה הוא בסופו של תהליך רב-שלבי הדורש אימון ואופטימיזציה של רשתות NN על מסגרות-עבודה באמצעות נתוני אימון זמינים או מותאמים-במיוחד. (מקור התמונה: Microchip Technology)

איור 1: מימוש מודל היסק עבור AI קצה הוא בסופו של תהליך רב-שלבי הדורש אימון ואופטימיזציה של רשתות NN על מסגרות-עבודה באמצעות נתוני אימון זמינים או מותאמים-במיוחד. (מקור התמונה: Microchip Technology)

מדוע מודלי היסק מאתגרים מבחינה חישובית

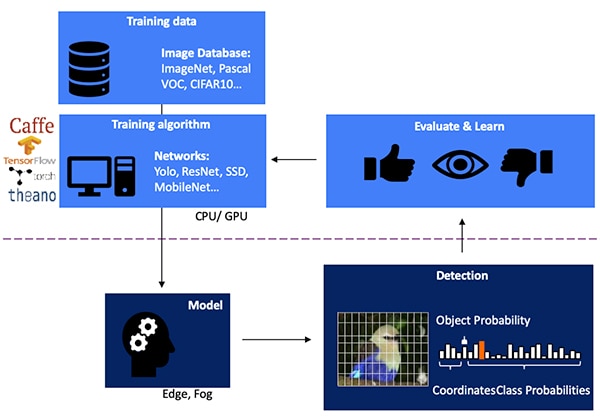

אף על פי שהגודל והמורכבות פחותים בהשוואה למודל ששימש בתהליך האימון, מודל היסק NN עדיין מהווה אתגר חישובי עבור מעבדים למטרות כלליות בשל מספר החישובים הרב שהוא דורש. בצורתו הגנרית, מודל NN עמוק כולל שכבות רבות של מערכים של נוירונים. בתוך כל שכבה ברשת מחוברת במלואה, כל נוירון ijn צריך לחשב את סך המכפלות של כל כניסה עם משקל ijw המשויך (איור 2).

איור 2: מספר החישובים הנדרשים עבור היסק עם NN מטיל עומס עבודה חישובי משמעותי. (מקור התמונה: Microchip Technology)

איור 2: מספר החישובים הנדרשים עבור היסק עם NN מטיל עומס עבודה חישובי משמעותי. (מקור התמונה: Microchip Technology)

באיור 2 לא מוצגת הדרישה החישובית הנוספת שמוטלת על ידי פונקציית ההפעלה המשנה את היציאה של כל נוירון עקב מיפוי ערכים שליליים לאפס, מיפוי ערכים הגדולים מ- 1 ל- 1, ופונקציות דומות. היציאה של פונקציית ההפעלה עבור כל נוירון ijn משמשת ככניסה לשכבה הבאה i+1, וכך הלאה בצורה זו עבור כל שכבה. לבסוף, שכבת היציאה של מודל NN מייצרת וקטור יציאה המייצג את ההסתברות שוקטור הכניסה המקורי (או המטריצה) תואם לאחת הקבוצות (Classes) (או התוויות) המשמשות בתהליך הלמידה המפוקח.

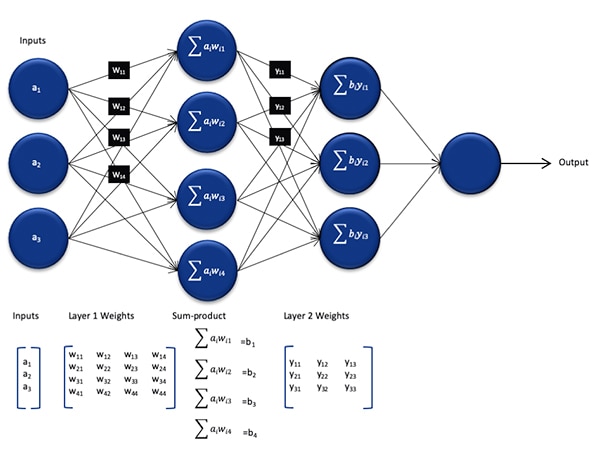

מודלים NN יעילים בנויים עם ארכיטקטורות גדולות ומורכבות בהרבה מהארכיטקטורה הגנרית המייצגת של NN המוצגת לעיל. לדוגמא, קונבולוציה NN טיפוסית (CNN) המשמשת לגילוי אובייקט תמונה מיישמת עקרונות אלו בחלקים, בסריקות לרוחב, לגובה ולעומק הצבע של תמונת הכניסה כדי לייצר סדרה של מפות מאפיינים המניבות לבסוף את וקטור חיזוי היציאה. (איור 3).

איור 3: מערכי CNN משמשים עבור גילוי אובייקט תמונה מערבים מספר גדול של נוירונים בשכבות רבות, ומטילים דרישות רבות יותר על פלטפורמת המחשוב. (מקור התמונה: Aphex34 CC BY-SA 4.0)

איור 3: מערכי CNN משמשים עבור גילוי אובייקט תמונה מערבים מספר גדול של נוירונים בשכבות רבות, ומטילים דרישות רבות יותר על פלטפורמת המחשוב. (מקור התמונה: Aphex34 CC BY-SA 4.0)

השימוש ב- FPGA להאצת החישובים המתמטיים של NN

למרות שממשיכות להופיע מספר אפשרויות לביצוע מודלי היסק בקצה, רק מעט אלטרנטיבות מספקות שילוב אופטימלי של גמישות, ביצועים ונצילות הספק הדרושים להיסק מעשי בקצה במהירות גבוהה. מבין האלטרנטיבות הזמינות עבור AI-קצה, רכיבי FPGA הם יעילים במיוחד מכיוון שהם יכולים לספק ביצועים עיליים מבוססי-חומרה של פעולות עתירות-מחשוב תוך צריכת הספק נמוכה יחסית.

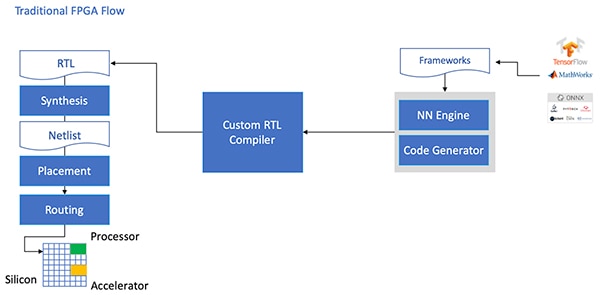

למרות יתרונותיהם, לעיתים מתעלמים מרכיבי FPGA עקב זרימת פיתוח מסורתית העלולה להרתיע מפתחים ללא ניסיון FPGA נרחב. כדי ליצור יישום FPGA יעיל של מודל NN שנוצר על ידי מסגרת-עבודה NN, המפתחים יצטרכו להבין את הניואנסים של המרת המודל לשפת העברת רגיסטר (RTL), תוך סינתזה של התכן והעבודה דרך המקום והנתיב הסופיים ודרך דרגת התכן הפיזי כדי לייצור מימוש ממוטב (איור 4).

איור 4: כדי לממש מודל NN ב- FPGA, המפתחים היו צריכים עד עתה להבין כיצד להמיר את המודלים שלהם ל- RTL ולעבוד דרך זרימת ה- FPGA המסורתית. (מקור התמונה: Microchip Technology)

איור 4: כדי לממש מודל NN ב- FPGA, המפתחים היו צריכים עד עתה להבין כיצד להמיר את המודלים שלהם ל- RTL ולעבוד דרך זרימת ה- FPGA המסורתית. (מקור התמונה: Microchip Technology)

עם רכיבי FPGA PolarFire, תוכנה מיוחדת והקניין הרוחני (IP) הקשור, חברת Microchip Technology מספקת פתרון ההופך היסק בקצה עם ביצועים עיליים בהספק נמוך לזמין באופן נרחב למפתחים ללא ניסיון ב- FPGA.

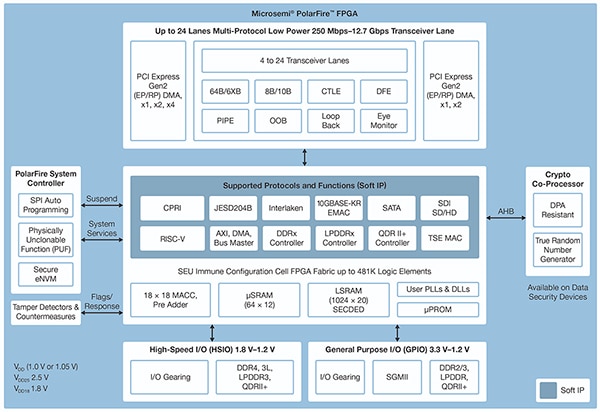

מיוצרים בטכנולוגיית תהליך לא-נדיף מתקדמת, רכיבי FPGA PolarFire מתוכננים למקסם את הגמישות והביצועים תוך הפחתת צריכת ההספק למינימום. לצד מערך נרחב של ממשקים במהירות גבוהה עבור תקשורת וכניסות/יציאות (I/O), הם כוללים מארג FPGA עמוק המסוגל לתמוך בפונקציונליות מתקדמת באמצעות ליבות IP תוכנה, כולל מעבדי RISC-V, בקרי זיכרון מתקדמים ותתי-מערכות אחרות של ממשקים סטנדרטיים (איור 5).

איור 5: ארכיטקטורת PolarFire מבית Microchip Technology מספקת מארג עמוק שתוכנן לתמוך בדרישות תכנים עם ביצועים עיליים, כולל מימוש מודל היסק עתיר-מחשוב. (מקור התמונה: Microchip Technology)

איור 5: ארכיטקטורת PolarFire מבית Microchip Technology מספקת מארג עמוק שתוכנן לתמוך בדרישות תכנים עם ביצועים עיליים, כולל מימוש מודל היסק עתיר-מחשוב. (מקור התמונה: Microchip Technology)

מארג FPGA PolarFire מספק מערך נרחב של אלמנטי לוגיקה ובלוקים מיוחדים, הנתמכים באמצעות מגוון של יכולות על ידי חלקים שונים ממשפחת ה- PolarFire FPGA, כולל סדרות MPF100T, MPF200T, MPF300T ו- MPF500T (טבלה 1).

|

טבלה 1: מגוון של מאפיינים ויכולות של מארג FPGA זמינים בסדרת PolarFire. (מקור הטבלה: DigiKey, מבוסס על גיליון הנתונים של PolarFire מבית Microchip Technology)

בין המאפיינים המעניינים במיוחד עבור האצת ההיסק, ארכיטקטורת PolarFire כוללת בלוק מתמטיקה ייעודי המספק פונקציית הכפלה-ואקומולציה (Multiply-Accumulate - MAC) של bit-18 × bit-18 עם קדם-מסכם (Adder). אופן מכפלה סקלרית (Dot Product) משתמש בבלוק מתמטיקה יחיד כדי לבצע שתי פעולות הכפלה של Bit-8 ומעניק מנגנון להגדלת הקיבולת הודות לניצול ההשפעה הזניחה של קוונטיזציית המודל על הדיוק.

בנוסף להאצת הפעולות המתמטיות, ארכיטקטורת PolarFire מסייעת להקל על הסוג של גודש זיכרון בו נתקלים בעת מימוש מודלי היסק על ארכיטקטורות למטרות כלליות, כגון זיכרונות מבוזרים קטנים לאחסון תוצאות ביניים שנוצרו במהלך ביצוע אלגוריתם NN. כמו כן, ניתן לאחסן את ערכי המשקל וה- Bias של מודל NN בזיכרון קריאה-בלבד (ROM) של עומק 16 על מקדמי Bit-18 הבנוי מאלמנטי לוגיקה הממוקמים בסמוך לבלוק המתמטיקה.

בשילוב עם מאפיינים אחרים של מארג PolarFire FPGA, בלוקי המתמטיקה מקנים את הבסיס עבור CoreVectorBlox IP ברמה גבוהה יותר מבית Microchip Technology. המארג משמש כמנוע NN גמיש המסוגל לבצע סוגים שונים של רשתות NN. לצד מערך של אוגרי בקרה, ה- CoreVectorBlox IP כולל שלושה בלוקי פונקציות עיקריים:

- מיקרו-בקר: מעבד תוכנה RISC-V פשוט הקורא את ה- (Binary Large Object (BLOB של קושחת Microchip ואת קובץ BLOB NN הספציפי של המשתמש מתוך אחסון חיצוני. הוא מבקר את כלל פעולות CoreVectorBlox על ידי ביצוע פקודות מה- BLOB של הקושחה.

- מעבד מטריקס (MXP): מעבד תוכנה הכולל שמונה יחידות לוגיקה אריתמטיות (ALU) של Bit-32 המתוכנן לבצע פעולות במקביל על וקטורי נתונים תוך שימוש בפעולות טנסור מסוג Element-Wise, כולל add, sub, xor, shift, mul, dotprod, ואחרות, עם דיוק של Bit-8, Bit-16 ו- Bit-32 מעורב, לפי הצורך.

- מאיץ CNN: מאיץ פעולות MXP באמצעות מערך דו-מימדי של פונקציות MAC הממומשות באמצעות בלוקי מתמטיקה ופועלות בדיוק של Bit-8.

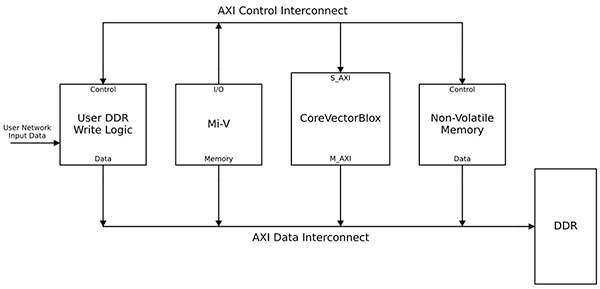

מערכת עיבוד NN שלמה תשלב בלוק CoreVectorBlox IP, זיכרון, בקר זיכרון ומעבד מארח, כגון ליבת מעבד תוכנת (Microsoft RISC-V (Mi-V (איור 6).

איור 6: בלוק CoreVectorBlox IP עובד עם מעבד מארח כגון מיקרו-בקר (Microsoft RISC-V (Mi-V למימוש מודל היסק NN. (מקור התמונה: Microchip Technology)

איור 6: בלוק CoreVectorBlox IP עובד עם מעבד מארח כגון מיקרו-בקר (Microsoft RISC-V (Mi-V למימוש מודל היסק NN. (מקור התמונה: Microchip Technology)

במימוש מערכת וידיאו, המעבד המארח יטען את ה- BLOB של הקושחה והרשת מתוך זיכרון Flash של המערכת ויעתיק אותם לזיכרון גישה אקראית (RAM) עם קצב נתונים כפול (DDR) לשימוש על ידי בלוק CoreVectorBlox. כשחבילות (Frames) הוידאו מגיעות, המעבד המארח כותב אותן לתוך זיכרון DDR RAM ומאותת לבלוק CoreVectorBlox להתחיל בעיבוד התמונה. לאחר הפעלת מודל ההיסק שהוגדר ב- BLOB הרשת, בלוק CoreVectorBlox כותב את התוצאות, כולל סיווג התמונות, חזרה ל- DDR RAM לשימוש על ידי יישום היעד.

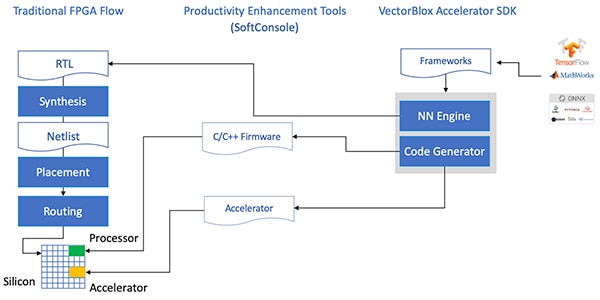

תזרים הפיתוח מפשט את מימוש NN FPGA

חברת Microchip חוסכת מהמפתחים את המורכבות של מימוש מודל היסק NN ברכיבי FPGA PolarFire. במקום להתמודד עם הפרטים של תזרים ה- FPGA המסורתי, מפתחי מודלי NN עובדים עם מסגרות-העבודה NN שלהם כרגיל וטוענים את המודל המתקבל לתוך ערכת פיתוח התוכנה (SDK) VectorBlox Accelerator מבית Microchip Technology. ערכת ה- SDK יוצרת את סט הקבצים הנדרש, כולל אלו הדרושים לתזרים פיתוח FPGA הרגיל ואת קובצי ה- BLOB של הקושחה ושל הרשת שהוזכרו לעיל (איור 7).

איור 7: ה- SDK VectorBlox Accelerator מנהל את הפרטים של מימוש מודל NN ב- FPGA, ויוצר אוטומטית את הקבצים הדרושים לתכנון ולהפעלת מודל ההיסק מבוסס-FPGA. (מקור התמונה: Microchip Technology)

איור 7: ה- SDK VectorBlox Accelerator מנהל את הפרטים של מימוש מודל NN ב- FPGA, ויוצר אוטומטית את הקבצים הדרושים לתכנון ולהפעלת מודל ההיסק מבוסס-FPGA. (מקור התמונה: Microchip Technology)

מכיוון שתזרים ה- SDK VectorBlox Accelerator מעביר את תכן ה- NN למנוע ה- NN הממומש ב- FPGA כשכבת-על (Overlay), רשתות NN שונות יכולות לפעול באותו תכן FPGA ללא צורך לבצע-מחדש את תזרים הסינתזה של תכן ה- FPGA. המפתחים יוצרים קוד ++C/C עבור המערכת המתקבלת ויכולים להחליף מודלים בתוך המערכת תוך כדי פעולה (On-the-Fly) או להפעיל מודלים בו-זמנית בחלונות זמן נפרדים.

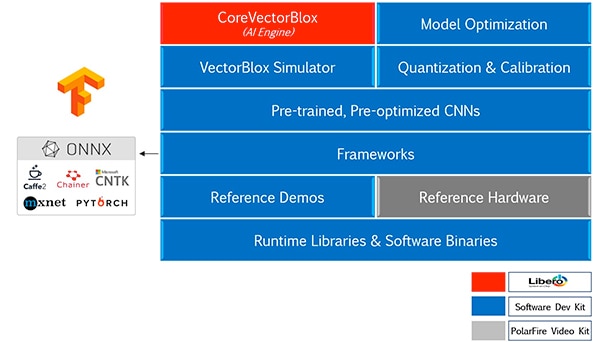

ה- VectorBlox Accelerator SDK ממזג את חבילת תכנון FPGA Libero מבית Microchip Technology עם מערך יכולות מקיף עבור פיתוח מודל היסק NN. לצד שירותי אופטימיזציה, קוונטיזציה וכיול המודל, ה- SDK מספק סימולטור NN המאפשר למפתחים להשתמש באותם קובצי BLOB כדי להעריך את המודל שלהם לפני השימוש בהם במימוש בחומרת FPGA (איור 8).

איור 8: ה- VectorBlox Accelerator SDK מספק מערך מקיף של שירותים המתוכנן למטב את מימוש FPGA של מודלי היסק מיוצרי-מסגרת-העבודה. (מקור התמונה: Microchip Technology)

איור 8: ה- VectorBlox Accelerator SDK מספק מערך מקיף של שירותים המתוכנן למטב את מימוש FPGA של מודלי היסק מיוצרי-מסגרת-העבודה. (מקור התמונה: Microchip Technology)

ה- VectorBlox Accelerator SDK תומך במודלים בפורמט (Open Neural Network Exchange (ONNX כמו גם במודלים ממספר מסגרות-עבודה כולל TensorFlow, Caffe, Chainer, PyTorch ו- MXNET. ארכיטקטורות CNN נתמכות כוללות MNIST, גרסות MobileNet, ResNet-50, Tiny Yolo V2 ו- Tiny Yolo V3. חברת Microchip פועלת להרחבת התמיכה כך שתכלול את מרבית הרשתות בקוד-פתוח של ערכת הכלים OpenVINO open model zoo של מודלים מאומנים-מראש, כולל Yolo V3, Yolo V4, RetinaNet ו- SSD-MobileNet, מבין רבים אחרים.

ערכת הוידאו מדגימה היסק FPGA

כדי לעזור למפתחים לעבור במהירות לפיתוח יישומי ראייה משובצים חכמים, Microchip Technology מספקת יישום מקיף לדוגמה המתוכנן לפעול על ערכת PolarFire FPGA Video and Imaging MPF300-VIDEO-KIT ותכן הייחוס של החברה.

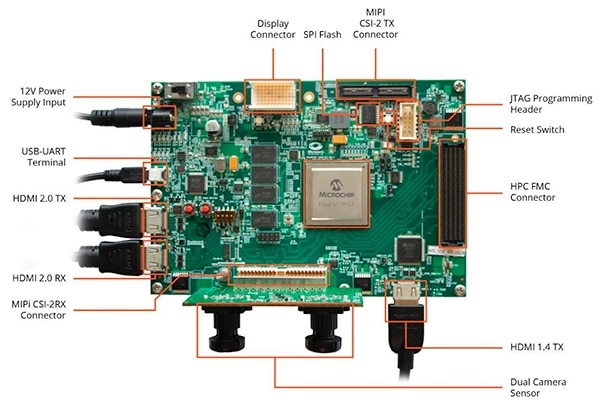

מבוסס על Microchip MPF300T PolarFire FPGA, הלוח של הערכה משלב חיישן מצלמה כפול, זיכרון RAM עם קצב נתונים כפול 4 (DDR4), זיכרון Flash, ניהול הספקת-כוח ומגוון של ממשקים (איור 9).

איור 9: ערכת PolarFire FPGA Video and Imaging MPF300-VIDEO-KIT והתוכנה הקשורה מספקים למפתחים התחלה מהירה להיסק מבוסס-FPGA ביישומי ראייה משובצת חכמה. (מקור התמונה: Microchip Technology)

איור 9: ערכת PolarFire FPGA Video and Imaging MPF300-VIDEO-KIT והתוכנה הקשורה מספקים למפתחים התחלה מהירה להיסק מבוסס-FPGA ביישומי ראייה משובצת חכמה. (מקור התמונה: Microchip Technology)

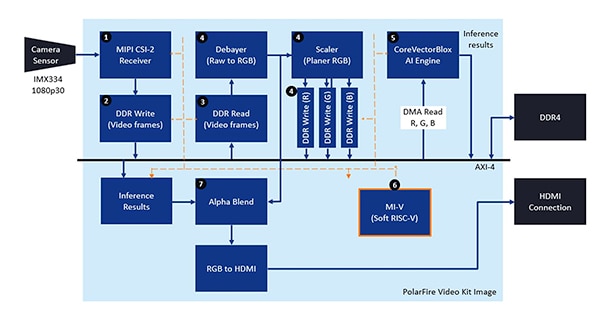

הערכה מגיעה עם פרויקט תכנון Libero שלם המשמש ליצירת קובצי הקושחה וה- BLOB של הרשת. לאחר תכנות קובצי ה- BLOB לתוך זיכרון Flash על-הלוח, המפתחים לוחצים על כפתור ההפעלה ב- Libero כדי להתחיל את ההדגמה, המעבדת תמונות וידאו מחיישן המצלמה ומציגה את תוצאות ההיסק בתצוגה (איור 10).

איור 10: ערכת PolarFire FPGA Video and Imaging מבית Microchip Technology מדגימה כיצד לתכנן ולהשתמש במימוש FPGA של ראייה משובצת חכמה הבנוייה סביב מנוע CoreVectorBlox NN מבית Microchip. (מקור התמונה: Microchip Technology)

איור 10: ערכת PolarFire FPGA Video and Imaging מבית Microchip Technology מדגימה כיצד לתכנן ולהשתמש במימוש FPGA של ראייה משובצת חכמה הבנוייה סביב מנוע CoreVectorBlox NN מבית Microchip. (מקור התמונה: Microchip Technology)

עבור כל מסגרת (Frame) של וידאו מהכניסה, המערכת מבוססת-FPGA מבצעת את הצעדים הבאים (עם מספרי הצעדים המתאימים לאיור 10):

- טעינת המסגרת מהמצלמה

- אחסון המסגרת ב- RAM

- קריאת המסגרת מה- RAM

- המרת התמונה הגולמית ל- RGB, Planer RGB, ואחסון התוצאה ב- RAM

- מעבד התוכנה Mi-V RISC-V מתניע את מנוע CoreVectorBlox, השולף את התמונה מתוך ה- RAM, מבצע היסק ומאחסן את תוצאות הסתברות הסיווג חזרה לתוך ה- RAM

- תוכנת Mi-V משתמשת בתוצאות כדי ליצור מסגרת שכבת-על עם תיבות תיחום, תוצאות הסיווג ומטא נתונים אחרים, ומאחסנת את המסגרת ב- RAM

- המסגרת המקורית ממוזגת עם מסגרת שכבת-העל ונכתבת לתצוגת HDMI

ההדגמה תומכת בהאצה של מודלים Tiny Yolo V3 ו- MobileNet V2, אך המפתחים יכולים להפעיל מודלים אחרים הנתמכים ב- SDK בשיטות שתוארו קודם לכן על ידי שינוי קוד קטן כדי להוסיף את שם המודל והאת המטא נתונים לרשימה הקיימת המכילה את שני מודלים של ברירת המחדל.

סיכום

אלגוריתמי AI כגון מודלים NN מטילים בדרך כלל עומסי עבודה עתירי-מחשוב הדורשים משאבי מחשוב חסונים יותר מאלו הזמינים במעבדים למטרות כלליות. בעוד שרכיבי FPGA מצוידים היטב כדי לעמוד בביצועים ובדרישות ההספק הנמוך של ביצוע מודל היסק, שיטות פיתוח FPGA קונבנציונליות יכולות להיראות מורכבות, ולעתים קרובות גורמות למפתחים לפנות לפתרונות לא-אופטימליים.

כפי שהוצג, באמצעות IP ותוכנות מיוחדות מבית Microchip Technology, מפתחים ללא ניסיון FPGA יכולים לממש תכנים מבוססי היסק המסוגלים לעמוד בדרישות הביצועים וההספק וכמו כן לעמוד בלוחות הזמנים.

מיאון אחריות: דעות, אמונות ונקודות מבט המובעות על ידי מחברים שונים ו/או משתתפי פורום באתר אינטרנט זה לא בהכרח משקפות את הדעות, האמונות ונקודות המבט של חברת DigiKey או את המדיניות הרשמית של חברת DigiKey.