מדוע וכיצד להשתמש ברכיבי Efinix FPGA עבור דימות AI/ML — חלק 1: צעדים ראשונים

באדיבות ‎העורכים האירופיים של DigiKey

2023-04-20

הערת העורך: גישות חדשות לארכיטקטורות FPGA מביאות בקרה עדינה יותר וגמישות גדולה יותר לענות על הצרכים של למידת מכונה (ML) ובינה מלאכותית (AI). חלק 1 של סדרת שני חלקים זו מציג ארכיטקטורה אחת כזאת מבית Efinix וכיצד להתחיל לעבוד איתה תוך שימוש בלוח פיתוח. חלק 2 דן בחיבור לוח הפיתוח להתקנים חיצוניים והיקפיים, כגון מצלמה.

רכיבי FPGA משחקים תפקיד קריטי ביישומים רבים, מבקרה תעשייתית ובטיחות עד רובוטיקה, תעופה וחלל ורכב. הודות לאופי הגמיש של ליבת הלוגיקה הניתנת לתכנות ויכולות ההתממשקות הרחבות שלה, אחד השימושים ההולכים וגדלים ברכיבי FPGA הוא עיבוד תמונה כשיש להשתמש בהיסק ML. רכיבי FPGA הם אידיאליים עבור מימוש פתרונות שיש להם מספר ממשקי מצלמה מהירות-גבוהה. נוסף לכך, רכיבי FPGA גם מאפשרים את המימוש של צינורות עיבוד ייעודיים בלוגיקה, ובכך להסיר צווארי בקבוק המשויכים לפתרונות מבוססי CPU או GPU.

עם זאת, עבור מפתחים רבים, היישומים שלהם דורשים יותר פונקציונליות ML/AI ובקרה או ניתוב עדין יותר ולוגיקה, מעבר למה שארכיטקטורות FPGA קלאסיות עם בלוקים לוגיים קומבינטוריים (CLBs) יכולים לספק. גישות חדשות יותר לארכיטקטורות FPGA מתמודדות עם נושאים אלה. לדוגמה, ארכיטקטורת Quantum של Efinix משתמשת ב-eXchangeable Logic ובלוק Routing (XLR).

מאמר זה דן בתכונות ומאפייני מפתח של ארכיטקטורת ה-Efinix FPGA, תוך הדגשת יכולות ה-AI/ML שלה והצגת יישומים מהעולם האמיתי. אחר כך הוא דן בלוח פיתוח וכלים נלווים בהם מפתחים יכולים להשתמש כדי להתחיל במהירות בתכנון דימות AI/ML.

התקני Efinix FPGA

Efinix מציעה כעת התקנים בשני תחומים. היא הציגה בהתחלה את משפחת ה-Trion, שמציעה צפיפויות לוגיות מ-4000 (4K) עד 120K אלמנטים לוגיים (LEs), ומיוצרת תוך שימוש בתהליך SMIC 40LL. קו ההתקנים החדש ביותר, משפחת ה-Titanium, מציע צפיפויות לוגיות מ-35K עד 1 מיליון (1M) אלמנטים לוגיים, ומיוצר בצומת TSMC 16-ננומטר (nm) הנפוץ מאוד.

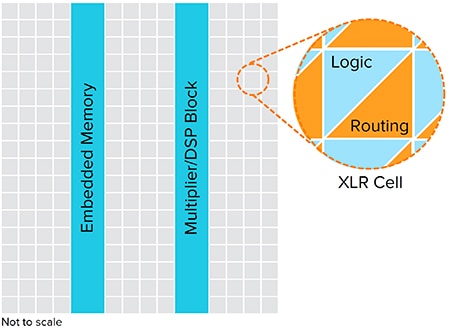

שני ההיצעים מבוססים סביב ארכיטקטורת ה-Quantum, שהיא ייחודית בעולם ה-FPGA. ארכיטקטורת FPGA הסטנדרטית מבוססת על בלוקים CLB שברמתם הפשוטה ביותר מכילים טבלת חיפוש (LUT) ופליפ-פלופים. בלוקים CLB מממשים משוואות לוגיות שמחוברות אחר כך באמצעות ניתוב. ארכיטקטורת Quantum של Efinix מתרחקת מלוגיקה מובחנת ובלוקים של ניתוב עם בלוק ה-XLR.

מה שעושה את בלוק ה-XLR ייחודי הוא שניתן להגדיר את תצורתו כך שיתפקד כתא לוגי עם LUT, אוגר ומסכם (Adder), או routing matrix. גישה זו מציעה ארכיטקטורה עדינה יותר המספקת גמישות ניתוב, מאפשרת מימושים שהם עמוסי לוגיקה או עמוסי ניתוב כדי להשיג את הביצועים המבוקשים.

איור 1: מה שעושה בלוק XLR לייחודי הוא שניתן להגדיר את תצורתו כך שיתפקד כתא לוגי עם LUT, אוגר ומסכם (Adder) או routing matrix. (מקור תמונה: Efinix)

איור 1: מה שעושה בלוק XLR לייחודי הוא שניתן להגדיר את תצורתו כך שיתפקד כתא לוגי עם LUT, אוגר ומסכם (Adder) או routing matrix. (מקור תמונה: Efinix)

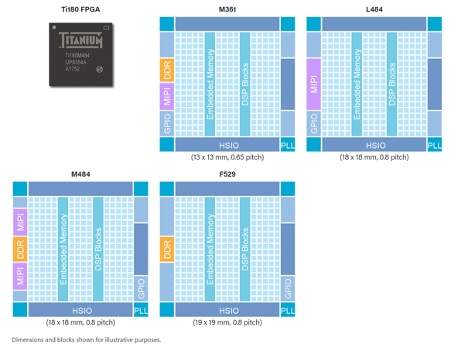

כמשפחה החדשה ביותר, התקני ה-Titanium מציעים את המאפיינים המתקדמים ביותר עבור המפתח (איור 2). ביחד עם ליבת ה-XLR, הם מספקים קישורים טוריים מרובי-Gigabit הפועלים במהירות של 16 גיגה-ביט לשנייה (Gbps) או 25.8 Gbps, תלוי בהתקן הנבחר. קישורים מרובי-Gigabit אלו הם חיוניים עבור אפשור העברת נתונים מהירות-גבוהה בשבב ומחוץ לשבב.

איור 2: ה-Titanium FPGA Ti180 מגיע במגוון אפשרויות, תלוי ברוחב האפיק, I/O ודרישות זיכרון. (מקור תמונה: Efinix)

איור 2: ה-Titanium FPGA Ti180 מגיע במגוון אפשרויות, תלוי ברוחב האפיק, I/O ודרישות זיכרון. (מקור תמונה: Efinix)

התקני Titanium גם מספקים מגוון רחב של יכולות התחברות כניסה/יציאה (I/O) הניתנות לחלוקה כ-I/O לשימוש כללי (GPIO), והיכולות לתמוך בתקני I/O קצה-יחיד (Single-Ended) כמו CMOS מתח-נמוך (LVCMOS) ב-3.3 וולט, 2.5 וולט ו-1.8 וולט.

עבור מהירות-גבוהה וממשק הפרשי, התקני ה-Titanium מספקים I/O מהירות-גבוהה (HSIO) התומך בתקני I/O קצה-יחיד (Single-Ended) כגון רכיבי LVCMOS ב-1.2 וולט, 1.5 וולט ו-SSTL ו-HSTL. תקני I/O הפרשי נתמכים על ידי HSIO כוללים איתות הפרשי מתח-נמוך (LVDS), SSTL הפרשי ו-HSTL.

רכיבי FPGA מודרניים דורשים גם זיכרון רוחב-פס-גבוה צמוד המשמש לאחסון מסגרות תמונה עבור יישומי עיבוד תמונה, נתונים לדוגמה עבור עיבוד אותות, וכמובן להרצת מערכות הפעלה ותוכנה עבור מעבדים ממומשים ב-FPGA. ההתקנים מסדרת Titanium מספקים את היכולת להתממשק עם קצב נתונים דינמי ארבע (DDR4) והספק-נמוך ((DDR4(x) (LPDDR4(x. בהתאם להתקן ה-Titanium המדויק הנבחר, תמיכת רוחב האפיק הוא x32 (J) או x16 (M), בעוד התקנים מסוימים לא נתמכים LPDDR4 (L).

רכיבי Titanium FPGA מבוססים SRAM ודורשים זיכרון תצורה, עם הגדרת התצורה של ההתקן מבוצעת על ידי master/slave Serial Peripheral Interconnect (SPI) או JTAG. כדי להבטיח ששיטת הגדרת תצורה זו היא מאובטחת, ה-Titanium FPGA משתמש בהצפנה AES GCM של ה-bitstream, ביחד עם AES GCM ו-RSA-4096 כדי לספק אימות bitstream. דרושה אבטחה חזקה כזו מאחר ורכיבי FPGA פרוסים בקצה היכן שגורמים זדוניים יכולים לגשת ולבצע מניפולציות בהתנהגותם.

הצגת לוח פיתוח

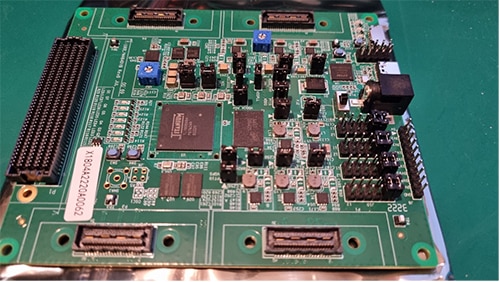

לוחות פיתוח מהווים אלמנט קריטי של תהליך הערכת ה-FPGA מאחר וניתן להשתמש בהם לחקירת היכולות של התקן ולבדוק אב-טיפוס של יישומים, ובכך לסייע בהפחתת סיכון כולל. לוח הפיתוח הראשון הקיים להערכת רכיבי Titanium FPGA ולהתחלת בנייה של יישומי אב-טיפוס הוא ה-Ti180 M484 (איור 3). הלוח כולל מחבר FPGA Mezzanine Card (FMC) וארבעה מחברי Samtec QSE.

איור 3: ביחד עם Titanium FPGA, ערכת הפיתוח Ti180 M484 כוללת מחבר FMC וארבעה מחברי Samtec QSE. (מקור תמונה: Adam Taylor)

איור 3: ביחד עם Titanium FPGA, ערכת הפיתוח Ti180 M484 כוללת מחבר FMC וארבעה מחברי Samtec QSE. (מקור תמונה: Adam Taylor)

ה-Ti180 FPGA הכלול בלוח פיתוח זה מספק 172K XLR תאים, 32 שעונים כלל-עולמיים, 640 אלמנטים של עיבוד אות דיגיטלי (DSP), ו-13 מגה-ביט (Mbits) של RAM משובץ. האלמנטים של DSP מספקים את היכולת לממש 19 x 18 הכפלות נקודה קבועה והכפלות 48-ביט. DSP זה יכול גם להיות ממוטב עבור פעולות פקודה יחידה, נתונים מרובים (SIMD) הרצות על קונפיגורציה כפולה או מרובעת. אלמנטים של DSP ניתנים גם להגדרת תצורה לבצע פעולות נקודה צפה.

כמו מרבית לוחות הפיתוח, לוח הפיתוח Ti180 מספק נורות LED ולחצנים פשוטים. עם זאת, החוזק האמיתי שלו בא מיכולות ההתממשקות שלו. לוח הפיתוח Ti180 מספק מחבר FMC מספר-פינים-נמוך המאפשר לחבר מגוון רחב של רכיבים היקפיים. מאחר והוא מהווה תקן הנמצא בשימוש נרחב, ישנם הרבה כרטיסי FMC המאפשרים חיבור ממיר אנלוגי-לדיגיטלי (ADC) מהירות-גבוהה, ממיר דיגיטלי-לאנלוגי (DAC), רשתות ופתרונות זיכרון/אחסון.

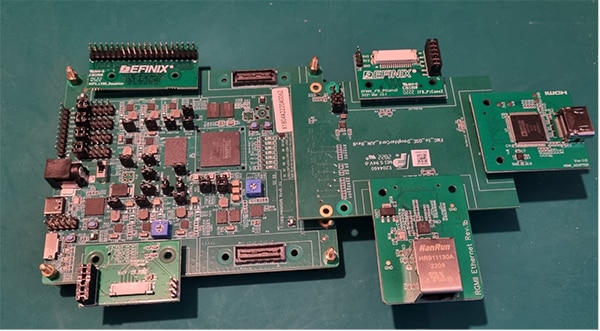

בנוסף לחיבור ה-FMC, הלוח מספק ארבעה מחברי Samtec QSE המאפשרים למפתח להוסיף כרטיסי הרחבה. מחברי QSE אלו משמשים לספק כניסות ויציאות MIPI, כשכל מחבר QSE מספק כניסת או יציאת MIPI.

איור 4: ערכת הפיתוח Ti180 M484 מוצגת עם המגוון הרב-תכליתי של אפשרויות הרחבה שלה המבוסס על מחברי QSE ו-FMC. (מקור תמונה: Adam Taylor)

איור 4: ערכת הפיתוח Ti180 M484 מוצגת עם המגוון הרב-תכליתי של אפשרויות הרחבה שלה המבוסס על מחברי QSE ו-FMC. (מקור תמונה: Adam Taylor)

לוח ה-Ti180 גם מספק 256 Mbits של LPDDR4 כדי לתמוך בזיכרון ביצועים-עיליים הדרוש ביישומי עיבוד אותות או תמונה. נוסף לכך, לוח הפיתוח מספק מגוון אפשרויות תזמון (Clocking) ב-25, 33.33, 50 ו-74.25 מגה-הרץ (MHz), שניתנות לשימוש עם חוג נעול הפאזה (PLL) של ההתקן כדי לחולל תדרים פנימיים שונים.

היכולת לתכנת מחדש ולנפות באגים באופן חי על הלוח במהלך פיתוח הוא קריטי ודורש חיבור JTAG, שמסופק על הלוח דרך ממשק USB-C. כמו כן מסופק זיכרון לא-נדיף בצורה של שני התקני 256-Mbit NOR Flash הניתנים לשימוש כדי להדגים את פתרון הגדרת התצורה.

הלוח מוזן ממתאם כוח אוניברסלי של 12-וולט הכלול בקופסה. כמו כן כלולים כרטיס break out FMC-ל-QSE, ביחד עם כרטיסי הרחבה מבוססי-QSE עבור HDMI, Ethernet, MIPI ו-LVDS. כדי להדגים את יכולות עיבוד התמונה של ה-Ti180, מסופקים גם כרטיס בת RPI כפול ושני כרטיסי מצלמה IMX477.

סביבת התוכנה

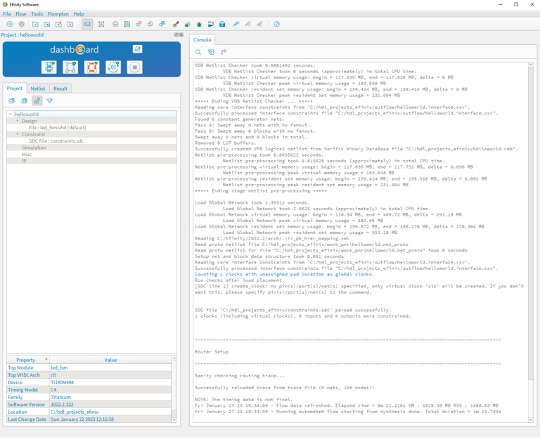

מימוש תכנון המכוון אל לוח הפיתוח Ti180 משתמש בתוכנת ה-Efinix Efinity. התוכנה מאפשרת את היצירה של bit stream באמצעות סינתזה ומיקום וניתוב. היא גם מספקת למפתחים בלוקים של קניין רוחני (IP), ניתוח תזמון וניפוי-באגים על-השבב.

שים לב שדרוש לוח פיתוח כדי לקבל גישה אל תוכנת ה-Efinity. אם כי, שלא כמו ספקים אחרים, לכלי אין גרסאות שונות הדורשות רישוי נוסף.

בתוך Efinity נוצרים פרויקטים חדשים המכוונים להתקן הנבחר. אחר כך ניתן להוסיף לפרויקט קבצי RTL, ואילוצים הנוצרים עבור תזמון ותכנון I/O. במסגרת Efinity מפתחים יכולים גם לממש את תכנון ה-I/O, תוך שימוש ב-HSIO, GPIO ו-I/O ייעודי.

איור 5: בתוך Efinity נוצרים פרויקטים חדשים המכוונים להתקן הנבחר. (מקור תמונה: Adam Taylor)

איור 5: בתוך Efinity נוצרים פרויקטים חדשים המכוונים להתקן הנבחר. (מקור תמונה: Adam Taylor)

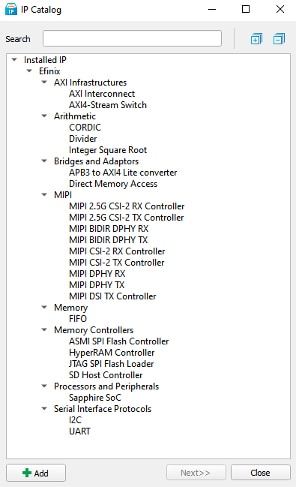

אלמנט קריטי של תכנון FPGA הוא מינוף IP, במיוחד עבור IP מורכב כמו חיברורי AXI, בקרי זיכרון ומעבדי softcore. תוכנת Efinity מספקת למפתחים מגוון בלוקים IP הניתנים לשימוש להאצת תהליך התכנון.

איור 6: Efinity מספקת למפתחים קטלוג IP שהם יכולים להשתמש בו להאצת תהליך התכנון. (מקור תמונה: Adam Taylor)

איור 6: Efinity מספקת למפתחים קטלוג IP שהם יכולים להשתמש בו להאצת תהליך התכנון. (מקור תמונה: Adam Taylor)

בעוד רכיבי FPGA מצוינים במימוש מבני עיבוד מקביליים, תכני FPGA רבים כוללים מעבדי softcore. אלה מספקים את היכולת לממש עיבוד סדרתי כגון תקשורת רשת. כדי לאפשר את הפריסה של מעבדי ה-softcore בהתקני ה-Efinix, Efinity מספקת את כלי הגדרת התצורה מערכת-על-שבב (SoC) Sapphire. מערכת-על-שבב (SoC) Sapphire מאפשרת למפתח להגדיר מערכת מרובת-מעבדים שיש לה אוספים של נתוני Cache ו-Cache Coherency לרוחב מעבדים מרובים, ביחד עם היכולת להריץ מערכת הפעלה Linux משובצת. בתוך Sapphire, המפתח יכול לבחור בין אחד וארבעה מעבדי softcore.

מעבד ה-softcore המיושם הוא ה-VexRiscV soft CPU, שמבוסס על ארכיטקטורת סט הפקודות RISC-V. מעבד ה-VexRiscv הוא יישום של bit-32 שיש לו הרחבות עבור חפיפה (pipelining) ומציע סט מאפיינים ניתנים להגדרת תצורה, דבר ההופך אותו לאידיאלי עבור מימוש בהתקני Efinix. תצורות אפשריות כוללות מכפל, פקודות אטומיות, הרחבות נקודה צפה ופקודות דחוסות. בהתאם להגדרת תצורה של מערכת ה-SoC, ביצועים ינועו בין 0.86 ו-1.05 DMIPS/MHz.

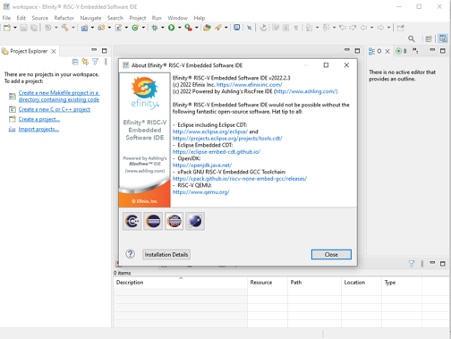

לאחר תכנון ויישום סביבת החומרה בהתקן ה-Efinix, ניתן לפתח את תוכנת היישום תוך שימוש ב-Ashling RiscFree IDE. ה-Ashling RiscFree היא IDE מבוססת-Eclipse המאפשרת את היצירה וההידור (compilation) של תוכנת יישום, ביחד עם ניפוי שגיאות על המטרה כדי לכוונן כוונון-עדין את היישום לפני פריסה.

איור 7: ה-Ashling RiscFree היא IDE מבוססת-Eclipse המאפשרת את היצירה וההידור (compilation) של תוכנת יישום, ביחד עם ניפוי שגיאות על המטרה. (מקור תמונה: Adam Taylor)

איור 7: ה-Ashling RiscFree היא IDE מבוססת-Eclipse המאפשרת את היצירה וההידור (compilation) של תוכנת יישום, ביחד עם ניפוי שגיאות על המטרה. (מקור תמונה: Adam Taylor)

אם מפתחים פתרון Linux משובץ, כל הארטיפקטים של אתחול הדרושים מסופקים, כולל First Stage Boot Loader, OpenSBI, U-Boot ו-Linux המשתמשת ב-Buildroot. לחלופין, המפתח יכול להשתמש ב-FreeRTOS אם דרוש פתרון זמן-אמת.

מימוש בינה מלאכותית (AI)

מימוש AI של Efinix בנוי על פעולת ה-RISC-V softcore. זה ממנף את יכולת ההוראה המותאמת-במיוחד של מעבד ה-RISC-V לאפשר את האצת הפתרונות TensorFlow Lite. השימוש במעבד RISC-V גם מאפשר למשתמשים ליצור הוראות מותאמות-במיוחד היכולות לשמש כחלק מהקדם-עיבוד או הלאחר-עיבוד בהמשך להיסק AI, תוך יצירת פתרון רספונסיבי ודטרמיניסטי יותר.

כדי להתחיל בצעדים ראשונים של מימוש AI, הצעד הראשון הוא לחקור את ה-Efinix model zoo, שהיא ספריה של דגמי AI/ML ממוטבת במיוחד עבור טכנולוגיית הקצה שלה. עבור מפתחים העובדים עם התקני ה-Efinix, ניתן לגשת אל ה-model zoo, ולאמן את הרשת תוך שימוש ב-Jupyter Notebooks או Google Colab. לאחר אימון הרשת, ניתן להמירה ממודל נקודה צפה לכמותי (quantized) תוך שימוש בממיר TensorFlow Lite.

כשבפורמט TensorFlow Lite, ניתן להשתמש במאיץ tinyML של Efinix כדי ליצור פתרון ניתן לפריסה על פתרון ה-RISC-V. מחולל ה-tinyML מאפשר למפתח להתאים-במיוחד את יישום המאיץ ולהפיק את קבצי הפרויקט. כשמופעל כך, ההאצה יכולה להיות בין 4x ו-200x, תלוי בארכיטקטורה הנבחרת ובהתאמה-המיוחדת.

מסקנה

התקני Efinix מספקים למפתחים גמישות הודות לארכיטקטורת XLR הייחודית שלהם. כלי התכנות toolchain מספקים את היכולת לא רק לממש תכן RTL, אלא גם לממש פתרונות SoC מורכבים הפורסים מעבדי softcore RISC-V. בנוי על גבי ה-softcore SoC נמצא פתרון AI/ML המאפשר פריסה של היסק ML.

מיאון אחריות: דעות, אמונות ונקודות מבט המובעות על ידי מחברים שונים ו/או משתתפי פורום באתר אינטרנט זה לא בהכרח משקפות את הדעות, האמונות ונקודות המבט של חברת DigiKey או את המדיניות הרשמית של חברת DigiKey.