מדוע וכיצד להשתמש ברכיבי Efinix FPGA עבור דימות AI/ML, חלק 2: צילום ועיבוד

באדיבות ‎העורכים האירופיים של DigiKey

2023-05-05

הערת העורך: גישות חדשות לארכיטקטורות FPGA מביאות בקרה עדינה יותר וגמישות גדולה יותר כדי לענות על הצרכים של למידת מכונה (ML) ובינה מלאכותית (AI). חלק 1 של סדרת שני חלקים זו מציג ארכיטקטורה אחת כזאת מבית Efinix וכיצד להתחיל לעבוד איתה תוך שימוש בלוח פיתוח. כאן, חלק 2 דן בחיבור לוח הפיתוח להתקנים חיצוניים והיקפיים, כגון מצלמה, וכיצד למנף את ה-FPGA כדי להסיר צווארי-בקבוק של עיבוד תמונה.

רכיבי FPGA משחקים תפקיד קריטי ביישומים רבים, מבקרה תעשייתית ובטיחות עד רובוטיקה, תעופה וחלל ורכב. הודות לאופי הגמיש של הליבה הלוגית הניתנת לתכנות ויכולות ההתממשקות הרחבות שלה, אחד השימושים ההולכים וגדלים ברכיבי FPGA הוא עיבוד תמונה, במקום שמשתמשים בלמידת מכונה (ML). רכיבי FPGA הם אידיאליים עבור מימוש פתרונות שהם בעלי מספר ממשקי מצלמה מהירות-גבוהה בשל המבנה הלוגי המקבילי שלהם. נוסף לכך, רכיבי FPGA גם מאפשרים את השימוש בצנרת עיבוד נתונים (processing pipeline) ייעודית בלוגיקה, ובכך להסיר צווארי בקבוק המשויכים לפתרונות מבוססי CPU או GPU.

מבט שני זה על רכיבי FPGA Titanium של Efinix יבחן את יישום הייחוס של עיבוד תמונה הבא עם לוח הפיתוח Ti180 M484 של ה-FPGA. המטרה היא להבין את החלקים המרכיבים של התכן, ולזהות היכן טכנולוגיית FPGA מאפשרת את הסרת צווארי הבקבוק או מאפשרת למפתחים יתרונות אחרים.

תכן הייחוס המבוסס על ה-Ti180 M484

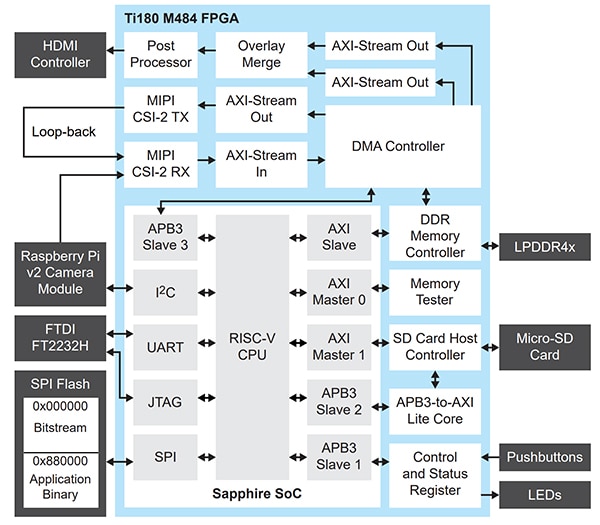

מבחינה קונספטואלית, תכן הייחוס (איור 1) מקבל תמונות ממספר מצלמות Mobile Industry Processor Interface (MIPI), מבצע אגירת מסגרות (frame buffering) ב-LPDDR4x, ואחר כך מוציא כפלט את התמונות לתצוגת ממשק מולטימדיה רזולוציה גבוהה (HDMI) . משתמשים בכרטיס FPGA Mezzanine (FMC) וארבעה ממשקי Samtec QSE על הלוח כדי לספק את כניסות המצלמה ויציאת HDMI.

איור 1: מבחינה קונצפטואלית, תכן הייחוס Ti180 M484 מקבל תמונות ממספר מצלמות MIPI, מבצע אגירת מסגרות (frame buffering) ב-LPDDR4x, ואחר כך מוציא כפלט את התמונות לתצוגת HDMI. (מקור תמונה: Efinix)

איור 1: מבחינה קונצפטואלית, תכן הייחוס Ti180 M484 מקבל תמונות ממספר מצלמות MIPI, מבצע אגירת מסגרות (frame buffering) ב-LPDDR4x, ואחר כך מוציא כפלט את התמונות לתצוגת HDMI. (מקור תמונה: Efinix)

משתמשים בכרטיס ההרחבה FMC ל-QSE בשיתוף עם כרטיס הבת HDMI כדי לספק את נתיב וידאו היציאה, בעוד ששלושה מחברי QSE משמשים להתחברות עם מצלמות ה-MIPI DFRobot SEN0494. אם אין מצלמות MIPI מרובות, ניתן להשתמש במצלמה יחידה תוך ניתוב חזרה למקור של ערוץ המצלמה היחידה כדי לבצע סימולציה של מצלמות נוספות.

ברמה גבוהה, יישום זה עשוי להיראות פשוט. עם זאת, קליטת תזרימי MIPI רזולוציה גבוהה (HD) בקצב מסגרות (frame rate) גבוה היא מאתגרת. כאן נמצא היתרון של טכנולוגיית FPGA, כי היא מאפשרת למתכננים להשתמש בתזרימי MIPI מרובים במקביל.

הארכיטקטורה של תכן הייחוס ממנפת מבני עיבוד מקבילי כמו גם עוקב באמצעות ה-FPGA. המבנים המקביליים משמשים למימוש צנרת עיבוד התמונה (image processing pipeline), בעוד מעבד RISC-V מספק את העיבוד העוקב המשמש עבור טבלאות החיפוש (LUTs) FPGA.

במערכות עיבוד תמונה מבוססות-FPGA רבות ניתן לפצל את צנרת עיבוד התמונה (image processing pipeline) לשני אלמנטים, כלומר תזרימי הכניסה והיציאה. תזרים הכניסה מחובר לממשק המצלמה/החיישן, ופונקציות עיבוד מיושמות על יציאת החיישן. פונקציות אלו יכולות לכלול המרת Bayer, איזון לבן (white balance) אוטומטי ושיפורים אחרים. בתזרים היציאה, מכינים את התמונה לתצוגה. זה כולל שינוי מרחבי צבע (color spaces) (לדוגמה, RGB ל-YUV) ועיבוד-נוסף לפורמט היציאה המבוקש, כמו HDMI.

לעיתים קרובות שרשרת עיבוד תמונת הכניסה עובדת בקצב שעון פיקסל החיישן. לעבודה זו יש תזמון שונה מלשרשרת היציאה, שמעובדת בתדר תצוגת היציאה.

מאגר מסגרות (frame buffer) משמש לחבר את הכניסה לצנרת עיבוד (processing pipeline) היציאה, שלרוב מאוחסן בזיכרון ביצועים-עיליים חיצוני, כמו LPDDR4x. מאגר מסגרות (frame buffer) זה חוצץ בין קווי צינורות הכניסה והיציאה, מאפשר גישה למאגר המסגרות באמצעות גישה ישירה לזיכרון בתדר שעון מתאים.

תכן הייחוס Ti180 משתמש בגישה דומה לעיקרון המתואר לעיל. קו צינורות עיבוד התמונה (image processing pipeline) כניסה מישם ליבת קניין רוחני (IP) מקלט MIPI Camera Serial Interface 2 (CSI-2), הבנויה על הכניסה/היציאה (I/O) בעלת יכולת שכבה פיזית MIPI (MIPI D-PHY) של ה-Titanium FPGA. ה-MIPI הוא ממשק מאתגר כי הוא משתמש באותות קצה-יחיד (single-ended) כמו גם הפרשיים על אותו זוג הפרשי, בנוסף לתקשורות מהירות-נמוכה ומהירות-גבוהה. שילוב ה-MIPI D-PHY בתוך ה-FPGA I/O מקטין את המורכבות של תכנון כרטיס המעגל תוך כדי הקטנת גם מפרט החומרים (BOM).

עם קבלת תזרים התמונה מהמצלמה, תכן הייחוס ממיר אחר כך את היציאה של ה-MIPI CSI-2 RX לתזרים Advanced eXtensible Interface (AXI). תזרים AXI הוא ממשק מהירות-גבוהה חד-כיווני המספק תזרים של נתונים מ-Master ל-Slave. אותות Handshaking להעברה בין Master ו-Slave מסופקים ביחד עם אותות Sideband. אותות Sideband אלו ניתנים לשימוש כדי להעביר מידע של תזמון תמונה כגון תחילת מסגרת (Frame) וסיום שורה (Line).

תזרים AXI הוא אידיאלי עבור יישומי עיבוד תמונה ומאפשר ל-Efinix לספק מגוון של IP עיבוד תמונה, שניתן אחר כך לשלב בקלות בשרשרת העיבוד כנדרש על ידי היישום.

לאחר קליטה, נתוני התמונה MIPI CSI-2 ואותות תזמון מומרים ל-AXI Stream ומועברים ככניסה למודול גישה ישירה לזיכרון (DMA), שכותב את מסגרת התמונה (image frame) ל-LPDDR4x ועובד כמאגר המסגרות (frame buffer).

מודול ה-DMA עובד תחת הבקרה של ליבת ה-RISC-V ב-FPGA בתוך מערכת-על-שבב (SoC) Sapphire. מערכת-על-שבב (SoC) זו מספקת בקרה, כמו עצירה והתחלה של מחזורי כתיבה DMA, בנוסף לאספקת המידע הנחוץ לערוץ כתיבה DMA לכתוב נכון את נתוני התמונה ל-LPDDR4x. זה כולל מידע על מיקום הזיכרון ורוחב וגובה התמונה מוגדרים בבייטים.

ערוץ היציאה בתכן הייחוס קורא את מידע התמונה ממאגר המסגרות (frame buffer) תחת הבקרה של ה-RISC-V SoC. הנתונים נפלטים מה-DMA IP כתזרים AXI, שמומר אחר כך מפורמט RAW המסופק על ידי החיישן לפורמט RGB (איור 2), ועובר הכנה ליציאה על ידי משדר ה-HDMI ADV7511 של Analog Devices שנמצא על הלוח.

איור 2: יציאת תמונות דוגמה מתכן הייחוס. (מקור תמונה: Adam Taylor)

איור 2: יציאת תמונות דוגמה מתכן הייחוס. (מקור תמונה: Adam Taylor)

השימוש ב-DMA גם מאפשר ל-Sapphire SoC RISC-V לגשת אל התמונות הנשמרות במאגר המסגרות (frame buffer), ואל הסטטיסטיקה המופשטת והמידע על התמונה. ה-Sapphire SoC גם מסוגל לכתוב רבדים (overlays) אל תוך ה-LPDDR4x כך שהם ניתנים למיזוג עם תזרים וידאו היציאה.

חיישני תמונה CMOS מודרניים (CISs) הם בעלי מספר אופני פעולה וניתנים להגדרת תצורה כך שיספקו עיבוד בשבב, ומספר פורמטים שונים של יציאה ותוכניות שעון. הגדרת תצורה זו מסופקת בדרך כלל דרך ממשק I²C. בתכן הייחוס Efinix, תקשורת I²C זו אל מצלמות ה-MIPI מסופקת על ידי מעבד ה-Sapphire SoC RISC-V.

אינטגרציה של מעבד ה-RISC-V בתוך ה-Titanium FPGA מקטין את הגודל הכולל של הפתרון הסופי מאחר והיא מסירה את הצורך במימוש שתי מכונות מצבים FPGA מורכבות המגדילות סיכון תכנון, כמו גם מעבדים חיצוניים המוסיפים למפרט החומרים (BOM).

הכללת המעבד גם מאפשרת תמיכה עם IP נוסף לתקשורת עם כרטיס ה-MicroSD. זה מאפשר יישומים של העולם-האמיתי היכן שיש צורך לאחסן תמונות עבור ניתוח מאוחר יותר.

באופן כללי, הארכיטקטורה של תכן הייחוס Ti180 ממוטבת כדי לאפשר פתרון קומפקטי, בעלות נמוכה, ועם זאת בעל ביצועים-עיליים המאפשר למפתחים להקטין עלות מפרט חומרים (BOM) באמצעות אינטגרציית מערכת .

אחד היתרונות העיקריים של תכני ייחוס הוא שניתן להשתמש בהם להתניע פיתוח יישומים על חומרה מותאמת-במיוחד, מאפשר למפתחים לקחת אלמנטים קריטיים של התכנון ולבנות בעזרתם פתרון עם ההתאמות המיוחדות הדרושות להם. זה כולל את היכולת להשתמש בתזרים TinyML של Efinix כדי לממש יישומי TinyML מבוססי-ראיה הרצים על ה-FPGA. זה יכול למנף את הטבע המקבילי של לוגיקת FPGA כמו גם את היכולת להוסיף בקלות הוראות מותאמות-אישית במעבדי RISC-V, דבר המאפשר את היצירה של מאיצים בתוך לוגיקת ה-FPGA.

מימוש

כפי שנדון בחלק 1, ארכיטקטורת ה-Efinix היא ייחודית בכך שהיא משתמשת בתאי eXchangeable Logic and Routing (XLR) כדי לספק ניתוב כמו גם פונקציונליות לוגית. מערכת וידאו כמו תכן הייחוס היא מעורבת, היא לוגית כמו גם כבדה בניתוב: דרושה לוגיקה נרחבת כדי לממש את מאפייני עיבוד התמונה, ודרוש ניתוב נרחב לחיבור תאי ה-IP בתדרים הדרושים.

תכן הייחוס משתמש בערך ב-42% של תאי ה-XLR בתוך ההתקן, משאיר מספיק מקום לתוספות, כולל יישומים מותאמים-במיוחד כגון ML קצה.

שימוש בבלוק ה-RAM ובלוקים של עיבוד אותות דיגיטלי (DSP) הוא גם כן יעיל ביותר, משתמש ב-4 מתוך 640 בלוקים DSP ו-40% מבלוקים הזיכרון בלבד (איור 3).

|

איור 3: הקצאת משאבים בארכיטקטורת ה-Efinix מראה שנעשה שימוש ב-42% מתאי ה-XLR בלבד, משאירה מספיק מקום לתהליכי עיבוד נוספים. (מקור תמונה: Adam Taylor)

ב-I/O של ההתקן, ממשק ה-DDR עבור ה-LPDDR4x משמש לספק את זיכרון היישום עבור ה-Sapphire SoC ומאגרי מסגרות התמונה (image frame buffers). כל משאבי ה-MIPI הייעודיים-להתקן מנוצלים יחד עם 50% מהחוגים נעולי הפאזה (איור 4).

|

איור 4: תמונת מצב של הממשק ומשאבי ה-I/O בהם משתמשים. (מקור תמונה: Adam Taylor)

ה-I/O למטרה כללית (GPIO) משמש לספק את תקשורת ה-I²C יחד עם חלק מהממשקים המחוברים ל-Sapphire SoC, כולל NOR FLASH, USB UART וכרטיס SD. ה-HSIO משמש לספק את יציאת הוידאו מהירות-גבוהה למשדר ה-ADC7511 HDMI.

אחד מהאלמנטים החיוניים כשמתכננים עם רכיבי FPGA הוא לא רק מימוש והתאמת התכן בתוך ה-FPGA, אלא גם להיות מסוגלים למקם את התכן הלוגי בתוך ה-FPGA ולהשיג את ביצועי התזמון הדרושים כשמנותבים.

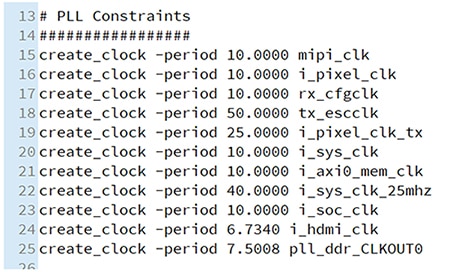

חלפו מזמן הימים של תכני FPGA בעלי תחום שעון יחיד. ישנם מספר שעונים שונים, כולם רצים בתדירויות גבוהות בתכן הייחוס Ti180. טבלת התזמון הסופית מראה את התדירויות המקסימליות שהושגו עבור השעונים בתוך המערכת. זהו היכן שביצועי התזמון המבוקשים יכולים גם להיראות באילוצים (איור 5), שהם בעלי תדר שעון מקסימלי של 148.5 מגה-הרץ (MHz) עבור שעון היציאה HDMI.

איור 5: אילוצי שעון עבור תכן הייחוס. (מקור תמונה: Adam Taylor)

איור 5: אילוצי שעון עבור תכן הייחוס. (מקור תמונה: Adam Taylor)

מימוש תזמון לעומת האילוצים מראה את הפוטנציאל של מבנה ה-Titanium FPGA XLR כמקצר את השהיית הניתוב האפשרית, ובכך משפר ביצועי תכן (איור 6).

|

איור 6: מימוש תזמון לעומת האילוצים מראה את הפוטנציאל של מבנה ה-Titanium FPGA XLR לקצר את השהיית הניתוב האפשרית, ובכך לשפר ביצועי תכן. (מקור תמונה: Adam Taylor)

מסקנה

תכן הייחוס Ti180 M484 מציג בבירור את היכולות של רכיבי Efinix FPGA ובמיוחד ה-Ti180. התכנון ממנף חלק ממבני ה-I/O הייחודיים למימוש נתיב עיבוד תמונה מורכב התומך במספר תזרימי MIPI נקלטים. מערכת עיבוד תמונה זו עובדת תחת הבקרה של Sapphire SoC ליבה-רכה, שמממש את האלמנטים של עיבוד עוקב הנחוצים של היישום.

מיאון אחריות: דעות, אמונות ונקודות מבט המובעות על ידי מחברים שונים ו/או משתתפי פורום באתר אינטרנט זה לא בהכרח משקפות את הדעות, האמונות ונקודות המבט של חברת DigiKey או את המדיניות הרשמית של חברת DigiKey.