What is the RP2350 High-Speed Transmit Interface (HSTX)?

2025-11-05 | By Maker.io Staff

Microcontrollers Raspberry Pi MCU

Maker-level MCUs and CPUs have commonly struggled with fast, consistent bit streaming. The RP2040 PIO made these problems easier to solve, enabling applications such as VGA and DVI video generation. The RP2350’s High-Speed Transmit Interface (HSTX) takes bit streaming to a whole new level, offering faster transmission rates and enabling more versatile use cases. This article examines HSTX’s inner workings and how it can unlock new possibilities for your projects.

High-Speed Transmissions on the RP2350

The HSTX is a new hardware peripheral, introduced with the RP2350 microcontroller, that powers the Raspberry Pi Pico 2. It’s a high-speed, serial, and output-only interface that supports double data rate (DDR) transmissions independent of the CPU clock. The peripheral can be viewed as an evolution of the previously introduced PIO interface—with higher data throughput and lower CPU involvement. This capability facilitates projects that were previously impossible on most development boards. Examples include high-speed memory interfacing and the generation of video signals, such as VGA and DVI.

RP2350 HSTX Main Features

The most important aspect of the new HSTX interface is that it requires minimal CPU involvement for data transmission and is independent of the main system clock. The interface’s maximum clock rate is capped at 150 MHz, which is the same as the CPU clock. However, since the HSTX interface can operate in double data rate (DDR) mode—transmitting two bits per pin and clock cycle—it achieves an effective maximum transmission rate of 300 MHz, or in other words, 300 Mb/s per pin.

GPIO pins 12 through 19 can operate as HSTX output channels. Image courtesy of Raspberry Pi

GPIO pins 12 through 19 can operate as HSTX output channels. Image courtesy of Raspberry Pi

The RP2350 supports HSTX on eight GPIO pins (GPIO 12 through 19), resulting in a maximum theoretical data transmission rate of 2.4 Gb/s. Further, the data output bits on the pins are guaranteed to be balanced within 300 ps.

How HSTX Works Under The Hood

Despite its impressive features, the HSTX interface is surprisingly easy to understand. The following block diagram, taken from section 12.11 of the official datasheet, explains the functional logic in great detail, including all possible control flag values and their meaning.

The functional block diagram of the HSTX interface in the RP2350. Image courtesy of Raspberry Pi (Section 12.11)

The functional block diagram of the HSTX interface in the RP2350. Image courtesy of Raspberry Pi (Section 12.11)

The HSTX hardware operates in a different clock domain, independent of the main system clock. An asynchronous FIFO buffer is responsible for decoupling the two separate domains while ensuring that the HSTX hardware doesn’t run dry, even at high output rates. The buffer offers eight input channels and operates at 32-bit in both domains. The FIFO is accessed via a separate bus interface from the control registers, which avoids bus stalls on DMA.

The subsequent command expander can be used to insert and interpret commands, allowing programs to manipulate the behavior of subsequent logic blocks in the pipeline. For that purpose, command op-codes and data need to be interspersed. It can only pop from the FIFO buffer once per clock cycle, resulting in an effective throughput that’s lower than the maximum theoretical data throughput. This issue is especially apparent in data-heavy commands and NOPs. It’s important to note that the command expander is active by default, but can be turned off using control registers. Doing so results in the data bypassing the command expander and going directly from the FIFO buffer into the output shifter.

The output shifter is required because the HSTX internally operates on 32-bit data. However, the output of the HSTX is no wider than 16 bits in DDR (two times eight bits; one per GPIO per clock cycle). Together with the bit crossbar, the output shifter is responsible for feeding the DDR output registers with the appropriate bits, which can either originate from the HSTX, PIO, or the HSTX’s internal clock generator. The control registers determine which signals get interspersed or whether any of them are inverted before being fed into the DDR output registers. It’s worth noting that the HSTX interface can operate in single data rate mode. The behavior can be changed via the control registers.

Comparisons to Other Popular Communication Methods

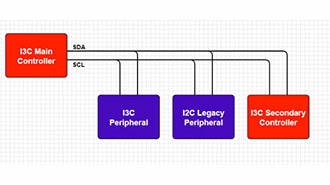

The high-speed TX interface’s main selling point is its speed and low CPU involvement. The interface operates in an independent domain, which distinguishes it from most other common communication mechanisms in the maker domain, such as SPI, UART, and I2C. Additionally, HSTX is purely a hardware interface, not limited by any communication protocols that would reduce effective data throughput. PIO, like HSTX, runs independently of the CPU core but is still clocked by the system clock (133 MHz on RP2040, 150 MHz on RP2350). However, PIO does not operate in DDR mode and cannot shift as many bits as HSTX. Although some edge cases allow incredibly high transmission rates similar to HSTX, most use cases are realistically limited to more modest maximum rates around 100 Mb/s, depending on the instructions. Furthermore, PIO requires more CPU and DMA involvement.

SPI and I2C are common standards that both have valid use cases. Still, compared to HSTX, both achieve much lower average throughput rates on the RP2350, with SPI having a raw, theoretical maximum rate of 133 Mb/s and I2C only managing to shift a maximum of 3.4 Mb/s. Practically, SPI and I2C both implement relatively complicated communication protocols with data overhead, resulting in lower effective data transmission rates and heavier CPU involvement.

UART’s effective throughput rate is even more limited, ranging between 100 kb/s up to about three Mb/s. Additionally, software UART requires heavy CPU involvement, further limiting the effective continuous throughput.

Summary

HSTX is a high-speed, output-only peripheral on the RP2350, designed to transmit data with minimal CPU involvement. It runs in its own clock domain, independent of the system clock, and can operate at up to 150 MHz. Using double data rate (DDR) mode, it achieves an effective maximum of 300 Mb/s per pin across eight pins (GPIO 12 to 19), with outputs balanced within 300 ps. Data flows through an asynchronous FIFO, decoupling the HSTX from the CPU, then through a command expander that can manipulate the data stream, and finally through a bit crossbar and output shifters that feed the output registers.

Compared to standard communication protocols like SPI, I2C, or UART, HSTX bypasses the overhead of framing, handshaking, and other protocol rules. This ability allows for much higher effective throughput and lower CPU load. Even though PIO provides flexible, bidirectional bit-banging, it’s still limited by the system clock and requires more CPU and DMA involvement. HSTX takes the concept further by providing a hardware-driven, high-speed interface that achieves higher transmission rates while keeping CPU overhead minimal. These reasons are what make HSTX ideal for tasks like high-speed memory interfacing or generating video signals.