כיצד להשתמש ב-FPGA ביישומים מוגבלי משאבים

באדיבות ‎DigiKey's North American Editors

2025-05-07

הצורך בלוגיקה ניתנת-להגדרה הולך וגובר במערכות משובצות מוגבלות משאבים. יישומים כגון AI קצה, ראיית מכונה ואוטומציה תעשייתית דורשים לוגיקה גמישה וספציפית ליישום כדי לעמוד בדרישות הביצועים המתפתחות תוך פעולה במסגרת מגבלות מחמירות של צריכת הספק, גודל ועלות. מערכי שערים הניתנים לתכנות בשטח (FPGA) מודרניים יכולים לענות על דרישות מתחרות אלו.

מאמר זה סוקר קריטריוני תכנון מרכזיים שיש לקחת בחשבון בעת בחירת FPGA עבור יישומים מוגבלי משאבים. לאחר מכן הוא מתאר כיצד קווי מוצרים שונים מתאימים עבור תרחישים ספציפיים באמצעות דוגמאות מפורטפוליו ה-FPGAs ממוטבי הספק ועלות של Altera. המאמר מסכם בהצגת ערכות פיתוח ולוחות הערכה בהם ניתן להשתמש כדי ליצור אב טיפוס ולתקף עקרונות תכנון.

שיקולים עבור בחירת FPGA

בחירת FPGA עבור מערכת מוגבלת משאבים כרוכה בבחינת מספר דרישות תכנון והתאמתן לפתרון הנכון. ישנם מספר מאפייני FPGA עיקריים שיש לקחת בחשבון:

קיבולת אלמנטי לוגיקה (LE): כאבן הבניין הבסיסית של FPGA, מספר ה-LE קובע כמה אלמנטי לוגיקה מותאמת-במיוחד ניתן לממש. מספרים גדולים יותר מאפשרים תכנים מורכבים יותר: הפשרה היא הגדלת ההספק, העלות וגודל המארז.

I/O וזיכרון: FPGAs משמשים לעתים קרובות לחיבור רכיבים שונים בתוך מערכת, ולכן מספר פיני ה-I/O מהווה שיקול עיקרי. כדי לשפר את ביצועי ה-I/O, FPGA רבים משלבים בלוקי לוגיקה קבועה מוקשחים עבור ממשקים כגון PCI Express (PCIe), זיכרון במהירות גבוהה ומקמ"שים רבי-ג'יגה-ביט.

בנוסף, כמה FPGAs משלבים מאפיינים כגון ממירי אנלוגי-לדיגיטלי (ADCs) וזיכרון Flash. שיפורים אלה יכולים להפחית את הצורך בשבבים נלווים, לחסוך מקום בלוח ולשפר את נצילות ההספק.

שילוב מעבדים: במקום להשתמש במעבד חיצוני, ניתן ליישם יחידת מיקרו-מעבד (MPU) "רכה" בתוך ה-FPGA. גישה זו יכולה להפחית את חתימת-השטח של המערכת, אך היא מתאימה ביותר עבור יישומים עם עומסי עבודת MPU פחות תובעניים.

עבור יישומים הזקוקים למעבדי MPU מהירים ויעילים יותר, המתכננים יכולים לשקול FPGA עם מערכת מעבד קשיח (HPS) שתממש את ה-MPU כבלוק לוגיקה קבוע בתוך ה-FPGA.

מאיצי חומרה: FPGAs כוללים בדרך כלל בלוקים ייעודיים עבור עיבוד אותות דיגיטליים (DSP) המטפלים ביעילות במשימות עתירות מחשוב כמו בקרת תנועה. התקנים מתקדמים יותר עשויים לכלול בלוקי טנסור ייעודיים עבור עומסי עבודה של בינה מלאכותית. היכולות של בלוקי המאיצים הללו משתנות באופן משמעותי בין משפחות FPGA ויכולות להשפיע באופן דרמטי על ביצועי המערכת הכוללים.

אופטימיזציות של מארזים והספק: כמה FPGAs מתוכננים במיוחד כדי למזער את חתימת-השטח הפיזית והחשמלית שלהם. לדוגמה, הם עשויים להציע אופני שינה בעלי צריכת אנרגיה נמוכה.

כלים: יצירת לוגיקה מותאמת-במיוחד יכולה להיות אתגר לא פשוט, במיוחד עבור מתכננים מתחילים. כלים כמו תוכנת התכנון Quartus Prime של Altera התגלו כמייעלי תהליך.

Quartus Prime, הבנוי כדי להפוך תכן FPGA לנגיש יותר, מציע חוויה ידידותית למפתחים, קטלוג נרחב של בלוקי לוגיקה בנויים-מראש, ויכולת לחבר את בלוקי הלוגיקה הללו באופן אוטומטי. הכלי משתלב עם תזרימי פעולה פופולריים של בינה מלאכותית (AI) ולמידת מכונה (ML), ומאפשר למפתחים לפרוס מערכות הפעלה (OS) פופולריות כמו Linux ו-Zephyr על גבי FPGA.

יכולות כאלה יכולות להאיץ משמעותית תכנון FPGA, ולהפוך את מאפייני הכלי לשיקול קריטי בעת בחירת התקן.

מחשוב בעל ביצועים גבוהים עבור עומסי עבודה משובצים מתקדמים

כדי להמחיש כיצד דרישות התכנון משפיעות על בחירת FPGA, כדאי להתחיל עם יישומים מתקדמים הדורשים צפיפות מחשוב, רוחב פס ואינטגרציה יוצאי-דופן. דוגמאות לכך כוללות יישומי AI קצה מתקדמים ושערים (Gateways) תעשייתיים בעלי ביצועים גבוהים.

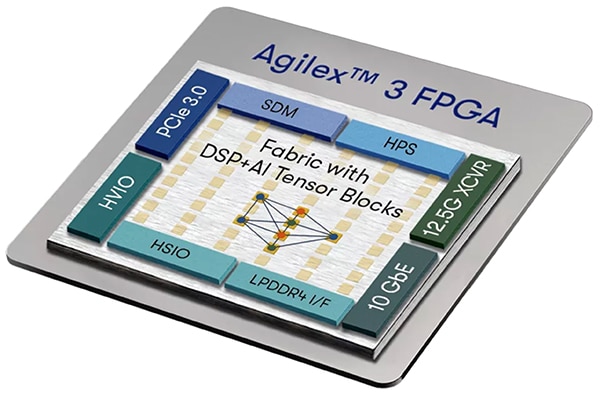

ה-FPGAs Agilex 3 (איור 1) מתוכננים לעמידה בדרישות יישומים אלו, ומציעים עד 135K LEs. השבבים זמינים הן בגרסאות FPGA-בלבד והן בגרסאות מערכת-על-שבב (SoC). התקני ה-SoC משלבים מעבד Cortex®-A55 ®Arm בעל שתי ליבות במהירות 800 מגה-הרץ (MHz), המאפשר ל-FPGA להתמודד עם חבילות תוכנה מורכבות כמו ממשקי אדם-מכונה (HMI) או חבילות תוכנת רשתות.

המארג הניתן-לתכנות כולל בלוקי AI Tensor המסוגלים לספק עד 2.8 INT8 טרה-פעולות בשנייה (TOPS). בלוקים אלה תומכים בפורמטי מחשוב שונים, כולל FP16, FP19, FP32 ו-BFLOAT16, והם ממוטבים עבור ביצוע יעיל של עומסי עבודה מבוססי AI. בלוקי DSP בעלי דיוק משתנה כלולים גם כן, ומעניקים ביצועים של עד 180 ג'יגה-פעולות-נקודה-צפה-לשנייה (GFLOPS) עבור עיבוד אותות למטרות כלליות.

איור 1: ה-Agilex 3 הולטת בזכות בלוקי ה-DSP וה-AI Tensor בעלי הביצועים הגבוהים שלה. (מקור התמונה: Altera)

איור 1: ה-Agilex 3 הולטת בזכות בלוקי ה-DSP וה-AI Tensor בעלי הביצועים הגבוהים שלה. (מקור התמונה: Altera)

חיבוריות במהירות גבוהה היא יתרון נוסף של ארכיטקטורת Agilex 3. המקמ"שים תומכים בקצבי נתונים של עד 12.5 גיגה-ביט-לשנייה (Gbits/s), עם בלוקי I/O מוקשחים הזמינים עבור PCIe 3.0, (GbE) Gigabit Ethernet 10, וממשקי זיכרון LPDDR4. הם תומכים בסינכרון זמן מדויק IEEE 1588 המשפר עוד יותר את התאמתו לרשתות תעשייתיות בזמן-אמת.

התקן A3CZ135BB18AE7S;מדגים את היכולות של משפחה זו. הוא כולל 135K LEs, 184 בלוקים DSP, ומעניק TOPS 2.54.

אינטגרציה מתקדמת עבור מערכות מורכבות

עבור יישומים כמו אוטומציה תעשייתית ומערכות ראייה לתחום הביניים, כוח מחשוב גולמי יכול להיות פחות חשוב מהיכולת לתמוך בתצורות מורכבות עם כמויות גדולות של לוגיקה מותאמת-במיוחד ו-I/O. FPGAs Cyclone V מתאימים היטב עבור תרחישים אלה, ומציעים עד LEs 300K וממשקים נרחבים במהירות גבוהה. כמו ה-Agilex 3, שבבים אלה זמינים בגרסאות FPGA-בלבד ובגרסאות SoC. במקרה זה, התקני ה-SoC משלבים מעבד Arm Cortex-A9 בעל שתי ליבות.

המארג הניתן-לתכנות בשבבים אלה כולל בלוקי DSP עם דיוק משתנה התומכים בכפל נקודה-קבועה של 9 × 9 משולש ו-18 × 18 כפול, וכפל נקודה קבועה או צפה של 27 × 27. בלוקים אלה יכולים לשמש עבור עיבוד אותות מתקדם ובינה מלאכותית.

תמהיל נרחב של I/O תומך במספר רמות מתח וסוגי ממשקים. בלוקי לוגיקה מוקשחים מאפשרים חיבוריות מתקדמת במהירות גבוהה, כולל PCIe 2.0, בקרי DDR3 ומקמ"שים הפועלים במהירות של עד Gbits/s 6.144.

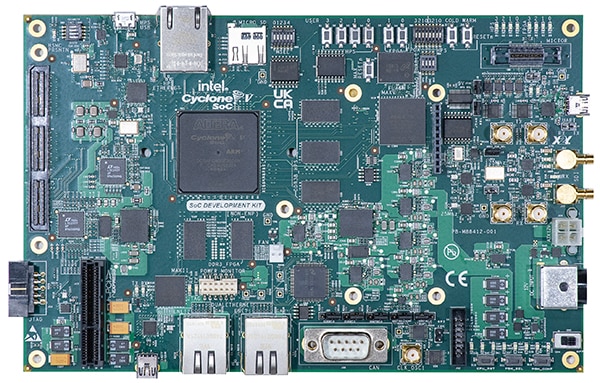

המפתחים יכולים להעריך את משפחת SoC Cyclone V באמצעות ערכת הפיתוח DK-DEV-5CSXC6N-B (איור 2). ערכה זו מיועדת עבור בניית אב-טיפוס מהירה של מערכות מורכבות בעלות תפוקה גבוהה.

איור 2: ערכת הפיתוח DK-DEV-5CSXC6N-B Cyclone V תומכת בבניית אבות-טיפוס בעלי ביצועים גבוהים. (מקור התמונה: Altera)

איור 2: ערכת הפיתוח DK-DEV-5CSXC6N-B Cyclone V תומכת בבניית אבות-טיפוס בעלי ביצועים גבוהים. (מקור התמונה: Altera)

הערכה כוללת מספר מאפיינים בולטים:

- שתי נקודות-חיבור Ethernet, מחבר PCIe x4 וכרטיס Mezzanine במהירות גבוהה (HSMC) עם 16 ערוצי LVDS בכל כיוון

- ממשקי USB 2.0 OTG, CAN, UART ושני ממשקי LCD לטקסט עם שתי-שורות

- זיכרון DDR3 SDRAM של 1 ג'יגה-בייט (Gbyte) לכל אחד משני צידי ה-FPGA וה-HPS, זיכרון Flash מרובע SPI של 128 מגה-בייט (Mbyte) וכרטיס microSD של 4 ג'יגה-בייט

הלוח כולל את התקן 5CSXFC5D6F31C8N, הכולל מעבד Arm Cortex-A9 עם שתי ליבות הפועל במהירות MHz 600, עם 85K LEs, 87 בלוקי DSP, ו-288 פיני I/O במארז FBGA-896 של 31 מ"מ × 31 מ"מ.

לוגיקה ניתנת-להגדרה חסכונית בהספק במארז קומפקטי

מגבלות חמורות סביב מקום וצריכת הספק מגדירות יישומים רבים. דוגמאות כוללות ממשקי חיישנים, תזמון הספקת-כוח ובקרה היקפית. במקרים אלה FPGAs כגון משפחת MAX 10 מציעים פתרון יעיל. התקני MAX 10 זמינים בתצורות של 2K עד 50K LEs ובמארזים הקטנים עד כדי 3 מ"מ × 3 מ"מ.

המאפיינים העיקריים כוללים עד שני ממירי ADC משולבים של bit-12, ממשק זיכרון DDR3 ובלוקי מכפיל התומכים באופני נקודה-קבועה של 18 × 18 ו-9 × 9 כפולים. זיכרון Flash על-שבב עם תמיכה באחסון תמונות כפולות מאפשר ל-FPGA להגדיר את עצמו ללא התקן זיכרון חיצוני.

יכולות חיסכון בהספק הן אחת התכונות הייחודיות ביותר של משפחת MAX 10. אופן שינה מובנה יכול להפחית את צריכת ההספק הדינמית עד 95%. הודות לזיכרון Flash מובנה בשבב, ניתן גם לכבות לחלוטין התקנים ולאחר מכן לחדש את פעולתם בפחות מ-10 מילישניות (ms).

אפשרות ספק-כוח יחיד מפשטת עוד יותר את הספקת-הכוח. זה הופך את התקני MAX 10 למתאימים במיוחד לתפקידי פיקוח, שבהם ייתכן שיהיה צורך להפעיל אשכולות הספקת-כוח לפני יתר המערכת.

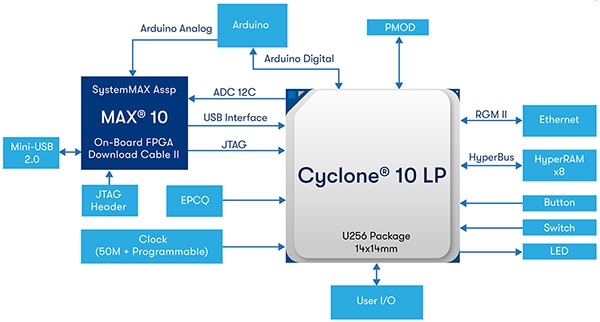

מפתחים המעוניינים ב-MAX 10 יכולים להעריך את המשפחה באמצעות לוח ההערכה MAX 10 FPGA EK-10M08E144 (איור 3). לוח זה מספק גישה לאותות חיצוניים דרך מחברי ונקודות בדיקה UNO R3 של Arduino, עם פריסה המתוכננת לתמוך במדידת ביצועי ADC והתנהגות הספקת-הכוח הכוללת.

איור 3: לוח ההערכה EK-10M08E144 MAX 10 FPGA מספק גישה נוחה ל-I/O העיקריים. (מקור התמונה: Altera)

איור 3: לוח ההערכה EK-10M08E144 MAX 10 FPGA מספק גישה נוחה ל-I/O העיקריים. (מקור התמונה: Altera)

הלוח כולל את התקן 10M08SAE144C8G, הכולל 8K LEs ו-ADC יחיד במארז LQFP בעל 144 פינים. בנוסף למשאבי החומרה המובנים שלו, FPGA זה תומך במעבד הרך Nios V מבוסס-RISC-V, המאפשר למתכננים למממש פונקציות בקרה קלות-משקל ללא צורך ביחידת מיקרו-בקר (MCU) חיצונית.

ביצועים מאוזנים עבור יישומים בתחום-הביניים

יישומים מסוימים דורשים יותר לוגיקה וקיבולת I/O מאשר ה-FPGAs ברמת-הבסיס יכולים לספק. דוגמאות לכך כוללות היתוך חיישנים, בקרת תנועה וגישור שבב-לשבב. FPGAs Cyclone 10 LP עונים על דרישות אלו הודות להיצע של עד 120K LEs ו-525 פיני I/O בהתקנים הממוטבים עבור הספק ורוחב-פס מאוזנים ביישומים רגישים-לעלות.

בדומה ל-MAX 10, המשפחה כוללת בלוקי DSP המתאימים לעומסי עבודה כגון סינון, חוגי בקרה והיסקי AI בסיסיים. בניגוד ל-MAX 10, התקני Cyclone 10 LP משלבים מקמ"שי LVDS אמיתי וסיומות על-שבב (OCT) כדי לתמוך בממשקים דיגיטליים במהירות גבוהה.

מפתחים המעוניינים ב-Cyclone 10 LP יכולים להעריך את המשפחה באמצעות ערכת ההערכה 10 Cyclone EK-10CL025U256 (איור 4). לוח זה מציע מחברי UNO R3 של Arduino ומחברי Pmod של Digilent עבור הרחבה קלה. מאפיינים אחרים כוללים GbE, USB 2.0, זיכרון SDRAM של 128 מגה-ביט (Mbits) וזיכרון Flash של Mbits 64.

איור 4: ערכת ההערכה EK-10CL025U256 Cyclone 10 תומכת בהרחבה קלה של רכיבים היקפיים. (מקור התמונה: Altera)

איור 4: ערכת ההערכה EK-10CL025U256 Cyclone 10 תומכת בהרחבה קלה של רכיבים היקפיים. (מקור התמונה: Altera)

הלוח כולל את התקן 10CL025YU256C8G, הכולל 25K LES, 66 בלוקי DSP ו-150 פיני I/O במארז של 14 מ"מ × 14 מ"מ. בדומה ל-MAX 10, משפחת Cyclone 10 LP תומכת במעבד הרך Nios V.

סיכום

למתכננים יש כיום גמישות רבה יותר מאי פעם בעת יישום לוגיקה מותאמת-במיוחד במערכות משובצות. יישומים בעלי ביצועים גבוהים יכולים להפיק תועלת מ-FPGAs עם מאיצי AI משולבים. תכנים בהספק-נמוך יכולים לנצל את היתרונות של אופני שינה. מערכות עתירות I/O יכולות למנף שבבים עם מספר פינים גדול וממשקים במהירות גבוהה. חשוב במיוחד לציין שאת כל היכולות הללו ניתן לממש במסגרת המגבלות המחמירות של מערכות משובצות מוגבלות-משאבים בעזרת ערכות קלות-לשימוש.

מיאון אחריות: דעות, אמונות ונקודות מבט המובעות על ידי מחברים שונים ו/או משתתפי פורום באתר אינטרנט זה לא בהכרח משקפות את הדעות, האמונות ונקודות המבט של חברת DigiKey או את המדיניות הרשמית של חברת DigiKey.